## **PRACTICAL WORKBOOK**

FOR ACADEMIC SESSION 2014

## ANALOG INTEGRATED CIRCUITS (EL-302) THIRD YEAR ELECTRONICS

Name:

Roll Number:

Class:

Batch:

Department :

Department of Electronic Engineering NED University of Engineering and Technology, Karachi

## LABORATORY WORKBOOK

### FOR THE COURSE

### **EL-302 ANALOG INTEGRATED CIRCUITS**

Prepared By:

Ms. Ayesha Akhtar (Lecturer)

Reviewed By:

Dr. Ghous Bakhsh Narejo (Associate Professor)

Approved By: THE BOARD OF STUDIES OF DEPARTMENT OF ELECTRONIC ENGINEERING

# ANALOG INTEGRATED CIRCUITS LABORATORY CONTENTS

| Lab No. | Date | List of Experiments                                                                                                                                                 | Page<br>No. | Remarks |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|

| 1       |      | Introduction to Mentor Graphics                                                                                                                                     | 1-4         |         |

| 2       |      | To learn how to use IC Studio of Mentor Graphics for IC<br>Designing                                                                                                | 5-12        |         |

| 3       |      | To determine the dc operating points of MOSFET operating in saturation region.                                                                                      | 13-17       |         |

| 4       |      | <ul> <li>To determine the behavior of MOS transistor using Mentor</li> <li>Graphics by analyzing its</li> <li>ID v/s VDs curve</li> <li>ID v/s VGs curve</li> </ul> | 18-22       |         |

| 5       |      | To determine the behavior of a Comm on Source Am plifier circuit using Mentor Graphics.                                                                             | 23-24       |         |

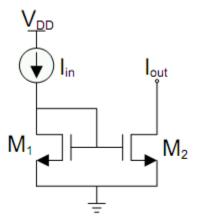

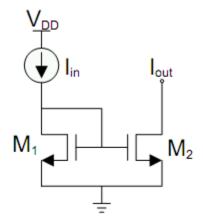

| 6       |      | Design and simulate simple MOS current mirror and current amplifier using Mentor Graphics.                                                                          | 25-27       |         |

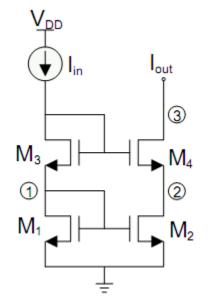

| 7       |      | Design and simulate cascade current mirror using Mentor Graphics.                                                                                                   | 28-30       |         |

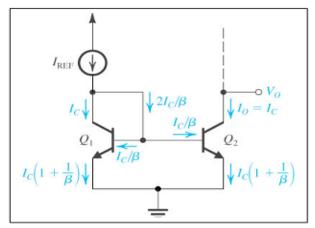

| 8       |      | To study different designs of constant current sources                                                                                                              | 31-39       |         |

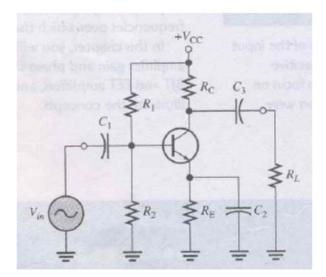

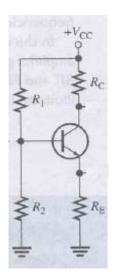

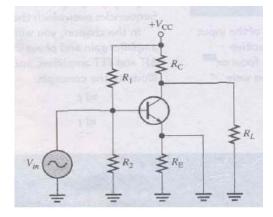

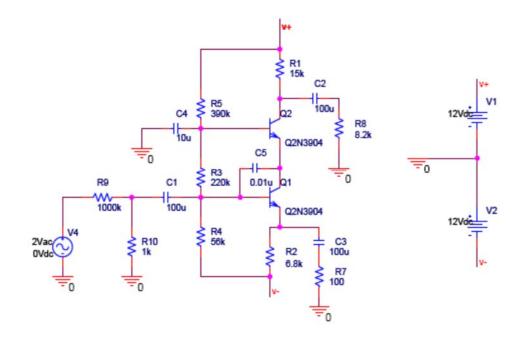

| 9       |      | To analyze the frequency response of Common Emitter<br>Amplifier.                                                                                                   | 40-47       |         |

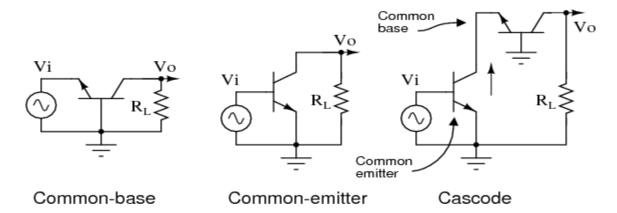

| 10      |      | To analyze the frequency response of Cascode Amplifier and compare it with Common Emitter Amplifier.                                                                | 48-51       |         |

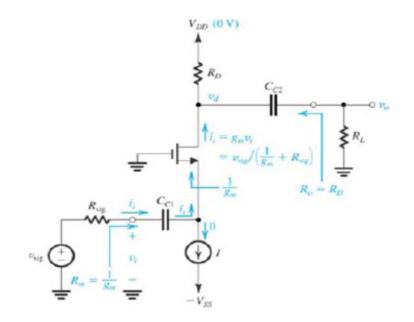

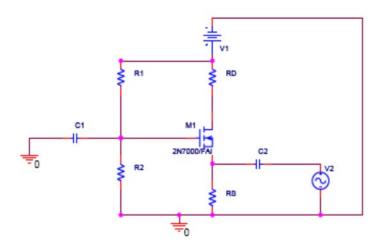

| 11      |      | Design and analyze a Common Gate Amplifier circuit.                                                                                                                 | 52-56       |         |

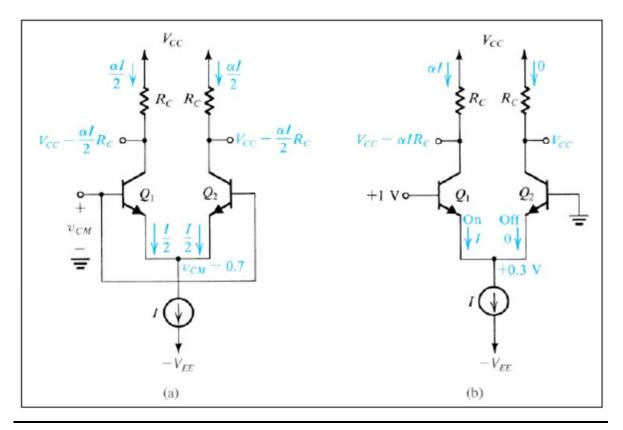

| 12      |      | To demonstrate the properties of differential amplifiers in both common mode and differential mode.                                                                 | 57-61       |         |

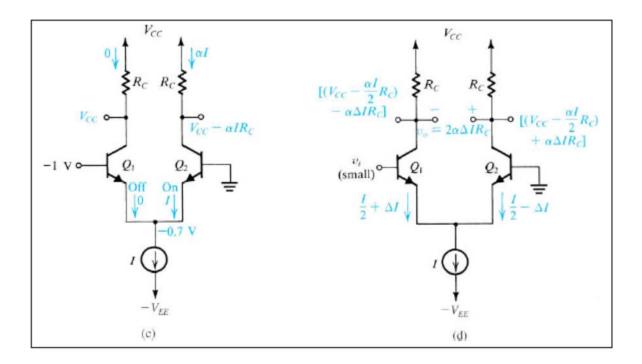

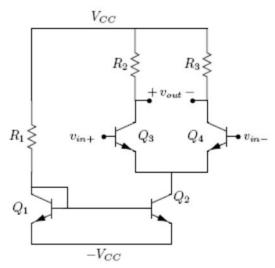

| 13      |      | To measure the open loop gain and offset voltage of an op amp.                                                                                                      | 62-65       |         |

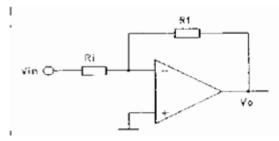

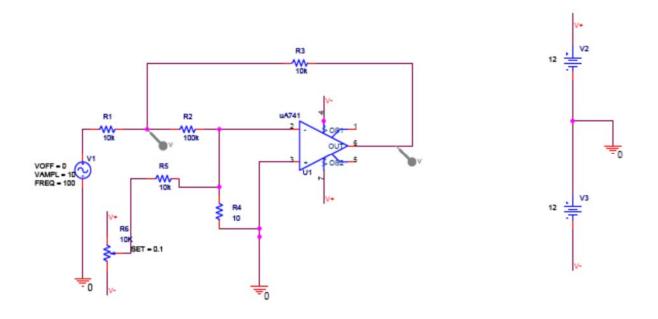

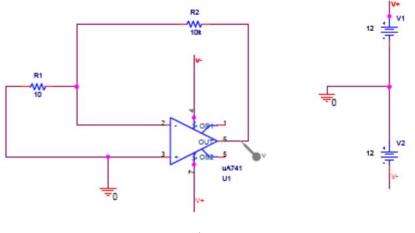

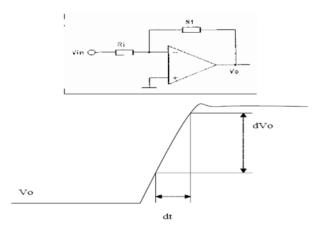

| 14      |      | To measure the slew rate and bandwidth of an op amp.                                                                                                                | 66-68       |         |

NED University of Engineering & Technology, Department of Electronic Engineering

### Lab No. 1

#### **INTRODUCTION:**

We will be working in three regions during AIC lab.

First of all you will be introduced to a new software i-e Mentor Graphics (IC Studio).

Secondly you people will have to implement labs on Orcad PSpice, which will the work done in pre-lab.

Thirdly you will be implementing circuits on bread board so as to get hands on experience.

Before coming to the introduction of Mentor Graphics let's have a look at the types of ICs:

#### **TYPES OF IC:**

- 1. Standard Product

- 2. Application Specific Integrated Circuit (ASIC)

- a) Full Custom

- b) Semi custom

#### 1. STANDARD PRODUCT:

A standard product is produced by the manufacturer for sale to the general public. Standard products are readily available for use by anybody for a wider range of applications.

#### 2. APPLICATION SPECIFIC INTEGRATED CIRCUIT (ASIC)

The term 'ASIC' stands for 'application-specific integrated circuit'. An ASIC is basically an integrated circuit designed specifically for a special purpose or application. Strictly speaking, this also implies that an ASIC is built only for one and only one customer. An example of an ASIC is an IC designed for a specific line of cellular phones of a company, whereby no other products can use it except the cell phones belonging to that product line. The opposite of an ASIC is a standard product or general purpose IC, such as a logic gate or a general purpose microcontroller, both of which can be used in any electronic application by anybody.

Aside from the nature of its application, an ASIC differs from a standard product in the nature of its availability. The intellectual property, design database, and deployment of an

NED University of Engineering & Technology, Department of Electronic Engineering

ASIC is usually controlled by just a single entity or company, which is generally the enduser of the ASIC too. Thus, an ASIC is proprietary by nature and not available to the general public.

#### a) <u>FULL-CUSTOM</u>

Full-custom ASIC's are those that are entirely tailor-fitted to a particular application from the very start. Since its ultimate design and functionality is pre-specified by the user, it is manufactured with all the photolithographic layers of the device already fully defined, just like most off-the-shelf general purpose IC's. The use of predefined masks for manufacturing leaves no option for circuit modification during fabrication, except perhaps for some minor fine-tuning or calibration. This means that a full-custom ASIC cannot be modified to suit different applications, and is generally produced as a single, specific product for a particular application only.

#### b) **SEMI-CUSTOM ASIC:**

Semi-custom ASIC's, on the other hand, can be partly customized to serve different functions within its general area of application. Unlike full-custom ASIC's, semi-custom ASIC's are designed to allow a certain degree of modification during the manufacturing process. A semi-custom ASIC is manufactured with the masks for the diffused layers already fully defined, so the transistors and other active components of the circuit are already fixed for that semi-custom ASIC design. The customization of the final ASIC product to the intended application is done by varying the masks of the interconnection layers, e.g., the metallization layers.

#### **INTRODUCTION TO MENTOR GRAPHICS:**

Mentor Graphics IC Studio is an EDA software .Electronic Design Automation (EDA or ECAD) is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips.

#### **TOOLS IN MENTOR GRAPHICS:**

- 1. Back end tools IC Nanometer Design- Category 1

- 2. Front end tools-Design Verification & Test- Category 2

- 3. PCB Tools PCB PADS- Category 3b

NED University of Engineering & Technology, Department of Electronic Engineering

We will be using the Back end tools

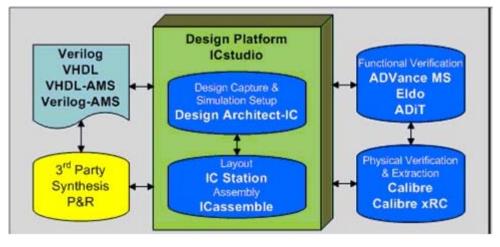

Fig 1.IC Nanometer Design

- **Design Architect-IC** A powerful tool for schematic capture, netlisting, simulation setup and results viewing.

- **IC Station** Provides the physical layout component of the Mentor Graphics full custom IC design flow. This suite includes application bundles for editing, schematic-driven layout, and top-level floor planning/routing.

- **IC assemble** A robust set of features for floor planning, top-level assembly and interactive routing.

- ADVance MS and ADVance MS RF A language-neutral, mixed-signal simulator that enables top-down design and bottom-up verification of multi-million gate analog/mixed-signal SoC designs.

- Eldo and Eldo RF An analog simulator offering numerous simulation and modeling options that deliver high-performance and high-speed simulation with the accuracy required by the user.

- **Calibre** The industry standard platform for physical verification, offering superior performance and capacity for both flat and hierarchical algorithms.

- CalibrexRC Accurate transistor-level, gate-level and hierarchical parasitic extraction.

NED University of Engineering & Technology, Department of Electronic Engineering

#### **TECHNOLOGY FILE**

The technology file contains process specific parameters such as layer thicknesses and the sheet resistance of the various layers.

**Mentor's Technology Design Kit** is a comprehensive and proven set of building blocks that enables semiconductor companies and electronics systems manufacturers to jump-start their design cycles using Mentor's analog/mixed-signal (AMS) IC Flow, thereby cutting time-to-market and ensuring manufacturing success of analog, RF and mixed-signal ICs and systems on chip (SoCs).

Mentor Graphics and GLOBALFOUNDRIES Semiconductor have teamed to develop TDKs for popular GLOBALFOUNDRIES manufacturing processes at multiple technology nodes, starting first with 0.18 micron. These AMS TDKs include all the foundry-specific data files and models for use with the Mentor Graphics integrated IC Flow comprised of the following tools: Design Architect-IC for schematic entry, Eldo and ADMS for analog and mixed-signal simulation, IC Station and IC assemble for schematic-driven layout and chip assembly, and Calibre for DRC/LVS verification and extraction.

NED University of Engineering & Technology, Department of Electronic Engineering

### Lab No. 2

#### **OBJECTIVE:**

To learn how to use IC Studio of Mentor Graphics for IC Designing

#### **EQUIPMENT REQUIRED:**

Linux and Mentor Graphics (IC Studio) installed PC

#### **THEORY:**

Mentor Graphics IC Studio is an EDA software .Electronic Design Automation (EDA or ECAD) is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips.

#### **PROCEDURE:**

#### Launching IC Studio:

Open a new terminal and type the following commands:

This will launch the window of ic\_studio as shown below:

NED University of Engineering & Technology, Department of Electronic Engineering

| -                                                           | ICstudio - «No Project» |  |

|-------------------------------------------------------------|-------------------------|--|

| <u>F</u> ile <u>E</u> dit <u>T</u> ocls <u>H</u> elp        |                         |  |

| ] 🖆 🕼 🙏 🖪 🛍 🗡 🚺 🚺                                           | <b>N</b> ?              |  |

| Selected:                                                   |                         |  |

| Litrary                                                     | Cell                    |  |

| Note: Reading user settings<br>Note: ICstudio startup compl | ete                     |  |

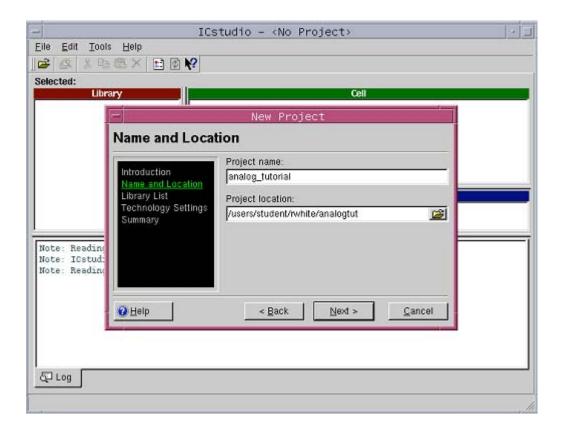

#### **Creating a Project:**

On the IC Studio window

- Click File>New>Project to create a new project.

- Click Next in the New Project pop-up window

- Enter the Project name (e.g project1) and the Project Location (home/student), click Next in the New Project popup window.

NED University of Engineering & Technology, Department of Electronic Engineering

#### **Specifying Location Map:**

On the next window that appears

- Click the **Open Location Map Editor** button. The Location Map Editor appears.

- To add the design kit's standard cell libraries to the library list Click Edit Menu > Add Standard MGC Libraries pull down menu item

- Add the MGC Design kit to the location map

- Click Edit Menu > Add MGC Design kit.

- Specify MGC Design Kit Path as

- The Library List editor looks as in the figure below.

- Click **OK** on the Library List Editor

- Click **Next** on the New Project pop-up window.

NED University of Engineering & Technology, Department of Electronic Engineering

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | New Project                                                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| dec | ted:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Library List                                                                                     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Introduction<br>Name and Location<br>Users U.M.<br>Technology Sections<br>Technology Sections    |

| _   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Summary Note: You may modify the library list later by using the Edit > Library List Editor menu |

| Į.  | - Library List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Editor                                                                                           |

| I   | Reg By Move Up 14340 David Del Rew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Der All Map Vars" Edit Menu - Ck   Nerd - Gancel                                                 |

| L   | Library Name Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                  |

| L   | And a second sec | tosSitcfpw_towe/wgc_icstd_ib/generic_ib/                                                         |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | icishtfov_tone/ngt_icitt_lb/device_ib 20 osSittfov_tone/ngt_icitt_lb/sources_ib 20               |

| 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Action_tomic/mgc_joint_jo/mgc_jc_veriog                                                          |

| 1   | and the second s | cflaw home/mpc, lostd lib/ingc ic commits 😅                                                      |

|     | 6 MGC_IC_COMMLIB. 06.1/app/2006.1_sus4oi5/cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Now_hame/mgc_icstd_ibs/mgc_ic_comm_qs 😅                                                          |

| L   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | flow_home/mgc_icstd_illa/mgc_ic_comm_if 🧱                                                        |

| I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | now_home/hgc_icstd_ib/mgc_ic_macrotib                                                            |

| l   | 9 MGC_DESIGN_KIT insp\/memtor-2004.3/ssVadk2_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>accept text change</li> </ul>                                                           |

|     | D Special Editing Keys: Escepe - abort text edit, Enter-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |

|     | D Special Editing Keys: Ecorpe - stort text edit, Enter-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |

|     | D Special Billing Keys: Escepe - abort test edit, Enter-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |

|     | D Special Editing Kays: Except - stort last edit, Errer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                  |

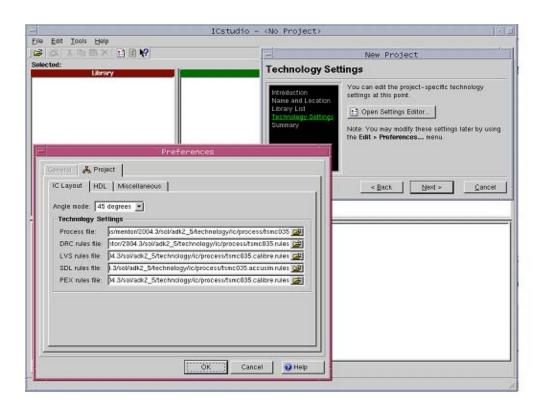

#### **Specifying Process files and other settings:**

- Click **Open Settings Editor** button. The **Project** tab of the **Preference**s dialog box appears

- Load the process file and rule files. Process file and rule files are present in

| Process file:   |

|-----------------|

| DRC rules file: |

| LVS rules file: |

| SDL rules file: |

| PEX rules file: |

|                 |

• Click **OK** on the Preferences dialog box.

NED University of Engineering & Technology, Department of Electronic Engineering

- Click Next on the New Project pop-up window

- View the **Summary** to make sure all the information is correct.

- Click Finish.

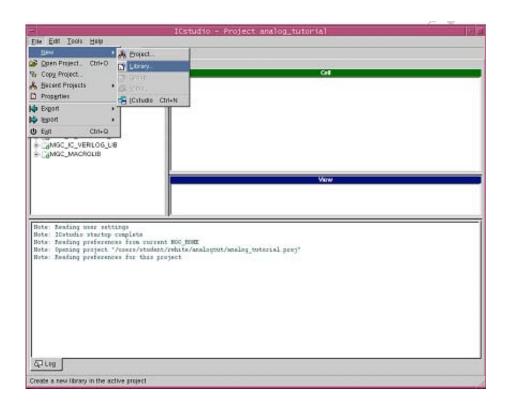

#### Creating a Library:

- Click **File >New > Library**. This opens the **Create Libr**ary dialogue box.

- Enter the name of the library you want to create (e.g. lib)

- Click OK.

The library appears in the IC Studio library pane as well as in the location map.

NED University of Engineering & Technology, Department of Electronic Engineering

#### **Capturing a Cell:**

To create a new Schematic cell:

- Select a library (e.g lib) where you want a cell view to be created.

- Click File > New >Cell View .The Create New View dialogue box appears

- Enter the **Cell Name** (e.g current source). If the cell does not exist, it is created.

- Specify the View Type as Schematic and click Finish.

Lab No.2

NED University of Engineering & Technology, Department of Electronic Engineering

| -                                                                                                                                                                                            | ICstudio - Project analog_tutorial                                                                                                   | 101 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Elle Edit Icols Help                                                                                                                                                                         |                                                                                                                                      |     |

| Selected: analogtut<br>Litrary<br>BMGC_DESIGN_KIT<br>BMGC_JC_COMMLIB<br>BMGC_JC_COMMLIB_OS<br>BMGC_JC_COMMLIB_RF<br>BMGC_JC_DEVICE_LIB<br>BMGC_JC_DEVICE_LIB                                 | Cell                                                                                                                                 | _   |

| <ul> <li></li></ul>                                                                                                                                                                          | Create New View                                                                                                                      |     |

| <pre>MGC_MACROLIB Mote: Reading user settings Note: IOStudio startup complete Note: Reading preferences from cur Mote: Opening project "/usecs/stud Note: Reading preferences for this</pre> | Library Name: analogtut<br>Cell Name: CommonSource<br>View Type: Schematic<br>Options<br>View Name: Schematic<br>Wew Name: Schematic |     |

| ۆت Log                                                                                                                                                                                       |                                                                                                                                      |     |

Design Architect (DA-IC) will open automatically where in you can capture the required cell design.

Analog Integrated Circuit NED University of Engineering & Technology, Department of Electronic Engineering

| 2    | 5 22 |      | ano F   | ΞQ.     | 9,8      | 图     | <b>F</b> | .* C    | 3     |         |      |        |       |       |  |        |          |        |      |              |

|------|------|------|---------|---------|----------|-------|----------|---------|-------|---------|------|--------|-------|-------|--|--------|----------|--------|------|--------------|

| t    | 0    | (11) | der ) ( | 00-1-20 | on in by | 2 90% | 40194    | ett 3 ¢ | 21.1  |         |      |        |       |       |  | (8.32) | 6, 1,833 | 25     | Hot  | Angen Ors    |

| 1    | -    |      |         |         |          |       | here     | Scr1 :  | maing | at / Co |      | Source | / Sch | erute |  |        |          | 1 0    | * 23 | scherwiic er |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Services     |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Library      |

| 8    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Skrudotion   |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        | -    | Dall         |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        | Pak      | rite - |      | Draw         |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Tutel        |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Check & Sm   |

| 8    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Select       |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Sy Property  |

| 1000 |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Unselect A   |

| 8    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Edit         |

| ij.  |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Move         |

| 1    |      |      |         |         |          |       |          |         |       |         | Σ    |        |       |       |  |        |          |        |      | Copy         |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Delote       |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Undo         |

| -    | - 8  | how  | /Hot    | Pale    | tte      |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Fig          |

| 1    |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Hatabi       |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Frapeties    |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Add          |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Instance     |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Wire         |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | But/Dundle   |

|      |      |      |         |         |          |       |          |         |       |         |      |        |       |       |  |        |          |        |      | Add Source   |

|      |      |      |         |         |          |       |          |         | Mes   | 5808    | Area | 2      |       |       |  |        |          |        |      | Property     |

|      |      |      |         |         |          |       |          |         |       |         |      |        | 1     |       |  |        |          |        |      | Home         |

| Ŀ    |      |      |         |         |          |       |          |         |       | -       |      |        |       |       |  |        |          |        |      | Instance     |

NED University of Engineering & Technology, Department of Electronic Engineering

### Lab No. 3

#### **OBJECTIVE:**

To determine the dc operating points of MOSFET operating in saturation region.

#### **EQUIPMENT REQUIRED:**

Linux and Mentor Graphics (IC Studio) installed PC

#### **THEORY:**

#### **Modes of operation of MOSFET:**

MOSFET can be operated in three modes:

1) Cut off

2) Triode

3) Saturation

To operate the MOSFET as a current source it needs to be operated in saturation region. For an N-MOS to operate in saturation region the operating conditions must be such that

$$v_{DS} \geq v_{GS} - V_t$$

Ideally the current that flows through the MOSFET in saturation region is independent of drain voltage and is given by:

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_t)^2$$

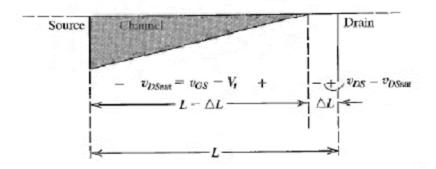

But practically increasing  $v_{DS}$  beyond  $v_{DS sat}$  causes the channel pinch off point to move slightly away from the drain towards the source which is as shown in figure 1:

NED University of Engineering & Technology, Department of Electronic Engineering

Figure 1: Increasing  $v_{DS}$  beyond  $v_{DS Sat}$  reduces the effective channel length.

Hence the voltage across the channel remains constant at  $v_{GS} - V_t = v_{DS sat}$  and the additional applied voltage applied to the drain appears as a voltage drop across the narrow deplition region between the end of the channel and the drain region. This voltage accelerates the electrons that reach the drain end of the channel and sweeps them across the depletion region into the drain.Now since  $i_D$  is inversely proportional to the channel length,  $I_D$  increases with  $V_{DS}$ .

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_t)^2 (1 + \lambda v_{DS})$$

#### **PROCEDURE:**

Launch IC Studio on Linux as explained in Lab Session 1.

#### **Capturing a Cell:**

- Select a library (e.g lib) where you want a cell view to be created.

- Click File > New > View. The Create New View dialog box appears.

- Enter the Cell Name (e.g current source) .If the cell does not exist, it is created.

- Specify the View Type as Schematic and click Finish.

NED University of Engineering & Technology, Department of Electronic Engineering

| 📤 Applications 🛛 Actions 😪 🥸                                         |                                                        | 🥥 Tue Nov 1, 1:20 AM 🄇 |

|----------------------------------------------------------------------|--------------------------------------------------------|------------------------|

| ×3                                                                   | ICstudio - Project dc_oper                             | iting 👘 👘              |

| <u>File E</u> dit <u>T</u> ools <u>H</u> elp                         |                                                        |                        |

| 🗳 🕼 👗 🖻 🕾 🗙 🚉 🖸 💔                                                    |                                                        |                        |

| Selected: my_lib                                                     |                                                        |                        |

|                                                                      | Library                                                | Cell                   |

|                                                                      |                                                        |                        |

|                                                                      |                                                        |                        |

| HMGC_IC_COMMLIB_QS<br>HMGC_IC_COMMLIB_RF                             | Create New View                                        | ×                      |

|                                                                      | View Type                                              |                        |

| MGC_IC_GENERIC_LIB                                                   | <b></b>                                                |                        |

|                                                                      | Library Name: my_lib                                   |                        |

| . GMGC_IC_VERILOG_LIB                                                | Cell Name: dc_operate                                  |                        |

|                                                                      | View Type: 🖻 Schematic 🔻                               |                        |

| ' <mark>``````````````````````````````````</mark>                    |                                                        |                        |

|                                                                      | Options                                                |                        |

|                                                                      | View Name: Schematic                                   |                        |

|                                                                      |                                                        |                        |

|                                                                      |                                                        | View                   |

|                                                                      |                                                        |                        |

|                                                                      |                                                        | 1                      |

|                                                                      | Pelp Back Nexts Einish C                               | incet                  |

|                                                                      |                                                        |                        |

| Woming, Veneming backing store                                       | disabled. This will lead to graphical redraw problems. |                        |

| Note: Reading user settings                                          |                                                        |                        |

| Note: Opening project "/home/stu<br>Note: Reading preferences from c |                                                        |                        |

| Note: Reading preferences for th                                     |                                                        |                        |

| Note: ICstudio startup complete<br>Note: Opening project "/home/stu  | ident/dc operating.proj"                               |                        |

| Note: Reading preferences for th                                     |                                                        |                        |

|                                                                      |                                                        |                        |

| δ⊒ Log                                                               |                                                        |                        |

| -                                                                    |                                                        |                        |

| a la la danta manter 147 (undance                                    | ntor-graphic/cali 🗱 ICstudio - Project dc_operating    |                        |

Design Architect (DA-IC) will open automatically where in you can capture the required cell design.

#### **Schematic Entry:**

• Select the parts for your schematic of the current source by choosing from a library of components.

To place the transistor on the sheet:

- In the palette on RHS click on Add Device and in select nmos.

- In the palette menu shown alongside, click on Library

- In the subsequent palette menu click on **Device Lib.**

- Select **ideal resistor** and place it on the sheet by clicking on the position you wish to place it. Click **BACK** to go to the IC Library palette and click on **Generic Lib.** Place **VDD**, **PORTOUT and Ground** on the sheet.

NED University of Engineering & Technology, Department of Electronic Engineering

- Add a DC source by selecting IC Library >Sources Library > DC. Highlight the DC Source, right click mouse, go to Properties > Edit to modify the voltage value of the source from 1V to 3.3V.

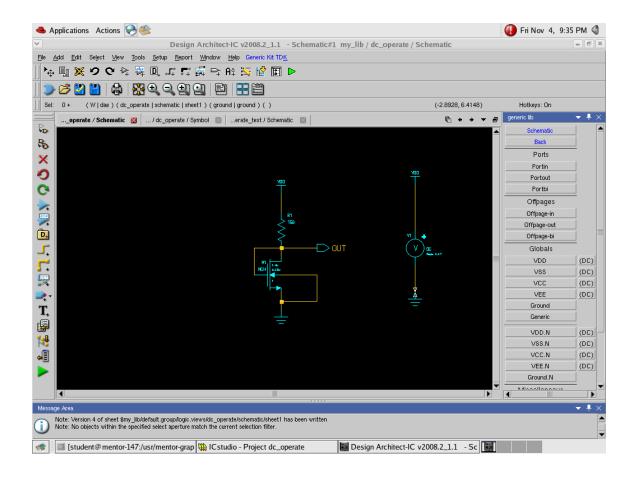

- From the **Schematic Edit Palette** select wire and wire the components as per the schematic shown below.

- Change the label **NET** of the **PORTOUT** symbol to **OUT**: Place cursor on **NET**, right click it then go to **Properties**. A display menu appears .Type **OUT** in the **Value** and click **OK**.

- To change the value of resistance place cursor on resistor, right click then go to **Properties**. A display menu appears, in it change the **value** to 150 and click **OK**.

- Click **Check & Save** from the **Schematic Edit Palette** or in the **Menu Bar** to check and save your sheet.

- Now click the simulation button.

NED University of Engineering & Technology, Department of Electronic Engineering

#### **Setting up the Simulation Parameters:**

Perform the simulation setup (all the ten steps) as explained in lab and view the dc operating points.

#### **RESULT:**

Attach the printout of the results i-e DC operating point of MOSFET operating in saturation region.

NED University of Engineering & Technology, Department of Electronic Engineering

### Lab No.4

#### **OBJECTIVE:**

To determine the behavior of MOS transistor using Mentor Graphics by analyzing its

- ID V/S VDS curve

- ID v/s VGs curve

#### **EQUIPMENT REQUIRED:**

Linux and Mentor Graphics (IC Studio) installed PC

#### **THEORY:**

The physical operation of a MOSFET can be divided into three regions of operation. For small value of V<sub>G</sub> the transistor is switched off. For an NMOS transistoras V<sub>G</sub>s increases from zero, holes in the p-substrate under the gate are repelled. Thus a depletion region is created from drain to source. For a sufficient value of interface potential, electron from source can actually travel through interface to drain terminal. The value of interface potential at this stage is called "Threshold Voltage" (Vt).

#### When VGS>Vt and VDS<(VGS - Vt): Triode of Linear Region

In this region of operation MOSFET operates like a resistor, controlled by the gate voltage relative to both the source and drain voltages. The current from drain to source is modeled as:

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_t) V_{DS} - \frac{V_{DS^2}}{2} \right]$$

where  $\mu_n$  is the charge-carrier effective mobility, *W* is the gate width, *L* is the gate length and *C*<sub>ox</sub> is the gate oxide capacitance per unit area.

#### When V<sub>GS</sub>>V<sub>t</sub> and V<sub>DS</sub>>(V<sub>GS</sub> - V<sub>t</sub>): Saturation Region

The switch is turned on, and a channel has been created, which allows current to flow between the drain and source. Since the drain voltage is higher than the gate voltage, the electrons spread out, and conduction is not through a narrow channel but through a broader, two- or three-dimensional current distribution extending away from the interface and deeper in the substrate. The onset of this region is also known as **pinch-off** to indicate the lack of channel region near the drain. The drain current is now weakly dependent upon drain voltage and controlled primarily by the gate–source voltage, and modeled very approximately as:

Lab No.4

NED University of Engineering & Technology, Department of Electronic Engineering

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_t)^2 (1 + \lambda V_{DS})$$

NED University of Engineering & Technology, Department of Electronic Engineering

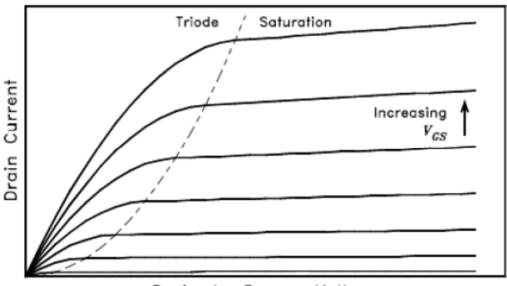

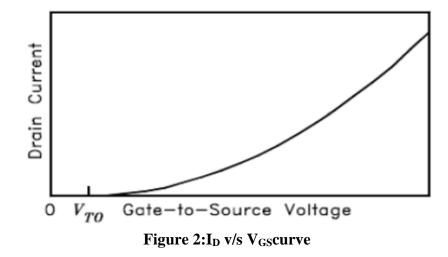

The characteristic curve of Fig. 1 indicates three regions of operation. The cutoff region, the triode region and the saturation region. The device is cutoff when VGs<Vt whereas it follows a linear relationship in triode region. The MOS operation, therefore, can be modeled as a linear resistor in triode region. Saturation region on the other hand is used when MOS is employed as an amplifier. In saturation region MOS provides a drain current which is independent of VDs and is determined by VGs according to a square law relationship. Thus Fig. 2 shows MOSFET operation as an ideal current source whose value is controlled by VGs.

#### PROCEDURE:

Launch IC Studio on Linux as explained in Lab Session 1.

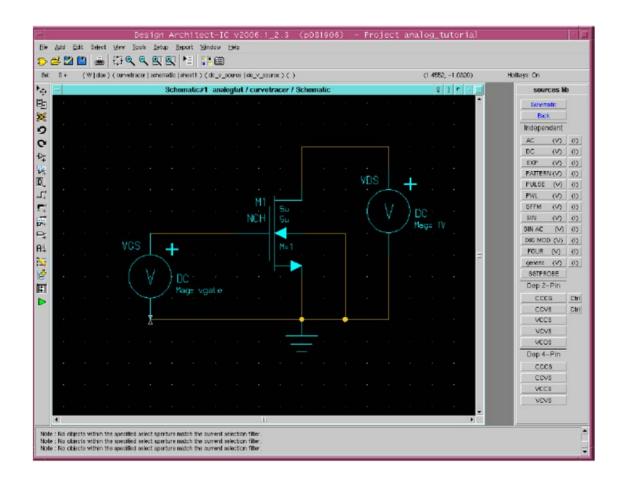

#### **Capturing a Cell and Schematic Entry:**

#### For ID v/s VDscurve:

Draw the following schematic by following the steps given in Lab Session 2.

NED University of Engineering & Technology, Department of Electronic Engineering

- In the circuit set the Instantaneous Value of source connected between gate and source as vgs and its dc value as vgate.

- Similarly set the instantaneous value of dc source connected between drain and source as vds and its dc value will be by default 1V.

#### **Setting up the Simulation Parameters:**

- Now perform step 1 to 4 of lab 2.

- Set the **Setup Analysis** as **DC** and then sweep vds,

#### **Defining Parameters:**

- Select Setup Outputs and goto

Parameter Sweeps

In Parameter Type select Global

Set Parameter as vgate and its value 0

Select Range type as linear and specify the range of vgate.

Add these parameters.

- Now perform steps 6, 7, 8 and 9 from lab 2.

#### Viewing the Results using EZWave Viewer:

• Under (*name of schematic*) open the List tab then drag the drain current to the waveform window.

#### ID v/s VGs curve:

Now implement changes in the schematic and simulation setup required. Also mention all the steps.

NED University of Engineering & Technology, Department of Electronic Engineering

#### **RESULT:**

Attach the printout of the results i-e

- ID v/s VDs curve

- ID v/s VGs curve

NED University of Engineering & Technology, Department of Electronic Engineering

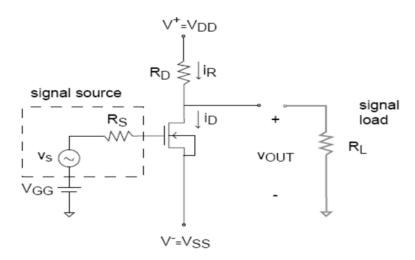

### Lab No.5

#### **OBJECTIVE:**

To determine the behavior of a Common Source Amplifier circuit using Mentor Graphics.

#### **EQUIPMENT REQUIRED:**

Linux and Mentor Graphics (IC Studio) installed PC

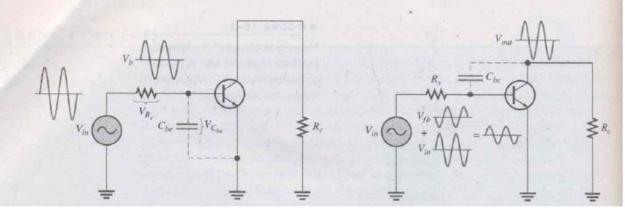

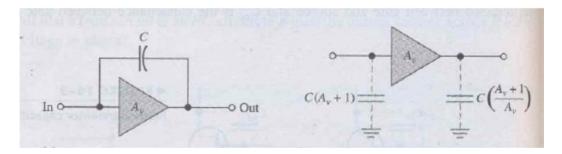

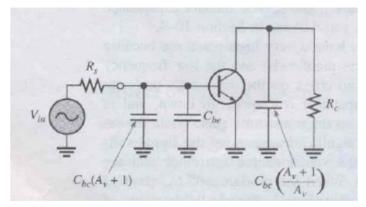

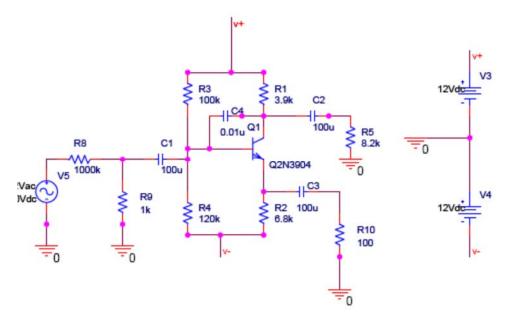

#### **THEORY:**