**Department of Electronic Engineering**

**NED University of Engineering and Technology**

Practical Work Book

**For the course**

**INTEGRATED CIRCUITS**

**(EL-202) For S.E (EL)**

**Instructor Name:**

---

**Student Name:**

---

**Roll No:** **Batch:**

---

**Semester:** **Year:**

---

**Department:**

---

**LABORATORY WORK BOOK

FOR THE COURSE**

**EL-202 INTEGRATED CIRCUITS**

Prepared and Reviewed By:

**Dr. Saleha Bano (Assistant Professor)**

and

**Ayesha Akhtar (Lecturer)**

Approved By:

**Board of Studies of Department of Electronic

Engineering**

# Integrated Circuits Laboratory Manual

## CONTENTS

| S.No. | Page No. | Date | Psychomotor Level | CLO | List of Experiments                                                                                                                                     | Sign. |

|-------|----------|------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.    | 1 - 4    |      | P3                | 3   | To OPERATE UNDER SUPERVISION the CMOS op-amp to determine CMRR.                                                                                         |       |

| 2.    | 5 - 10   |      | P3                | 3   | To PRACTICE NMOS Inverter circuit with resistive load and determine the noise margin with the help of its voltage transfer characteristics.             |       |

| 3.    | 11 - 14  |      | P3                | 3   | To OPERATE UNDER SUPERVISION the NMOS Inverter to determine its average power dissipation and TRY NMOS NAND gate and NMOS NOR gate with resistive load. |       |

| 4.    | 15 - 17  |      | P3                | 3   | To PRACTICE NMOS Inverter circuit with Enhancement load MOS and TRY the logic function $f = \overline{(a + b)c}$ .                                      |       |

| 5.    | 18 - 25  |      | P3                | 3   | To OPERATE UNDER SUPERVISION the CMOS Inverter circuit and determine its propagation delay and power dissipation.                                       |       |

| 6.    | 26 - 30  |      | P3                | 3   | To PRACTICE CMOS NAND gate and CMOS NOR gate and also TRY exclusive OR-gate (XOR) function.                                                             |       |

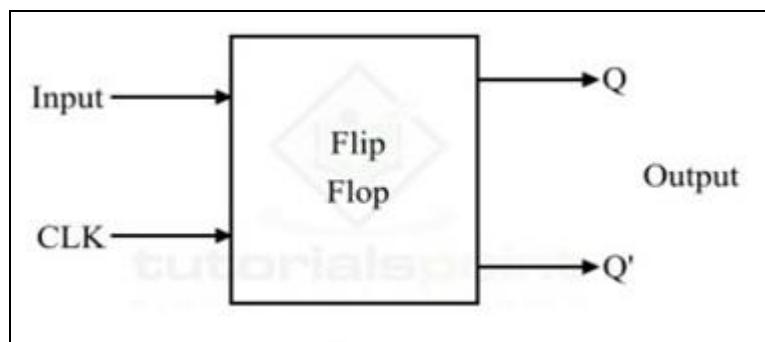

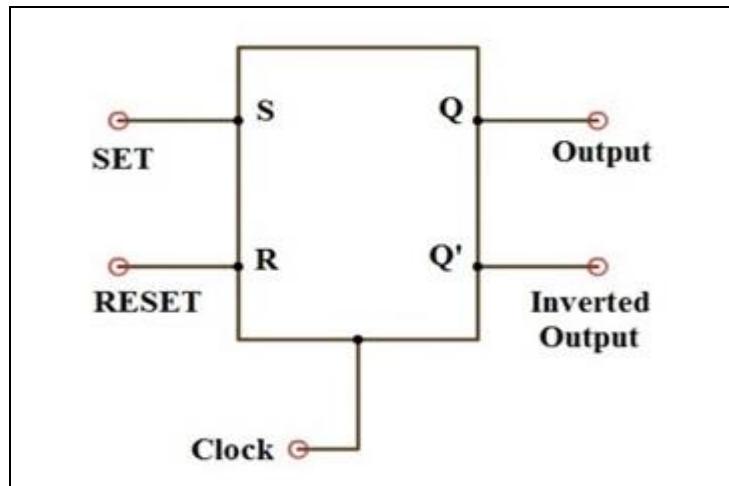

| 7.    | 31 - 37  |      | P3                | 3   | To OPERATE UNDER SUPERVISION SR Flipflop and D-Flipflop.                                                                                                |       |

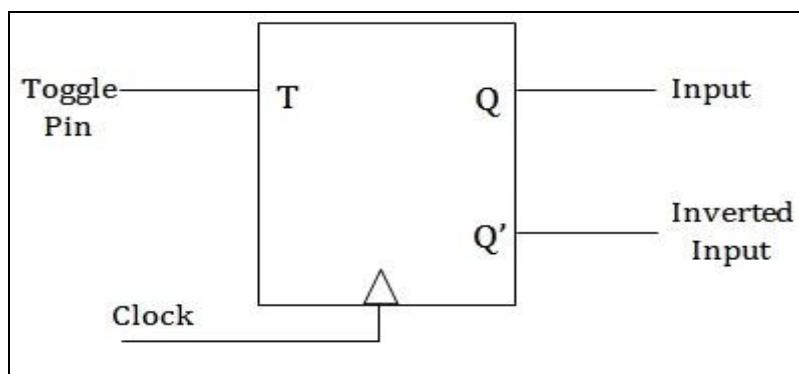

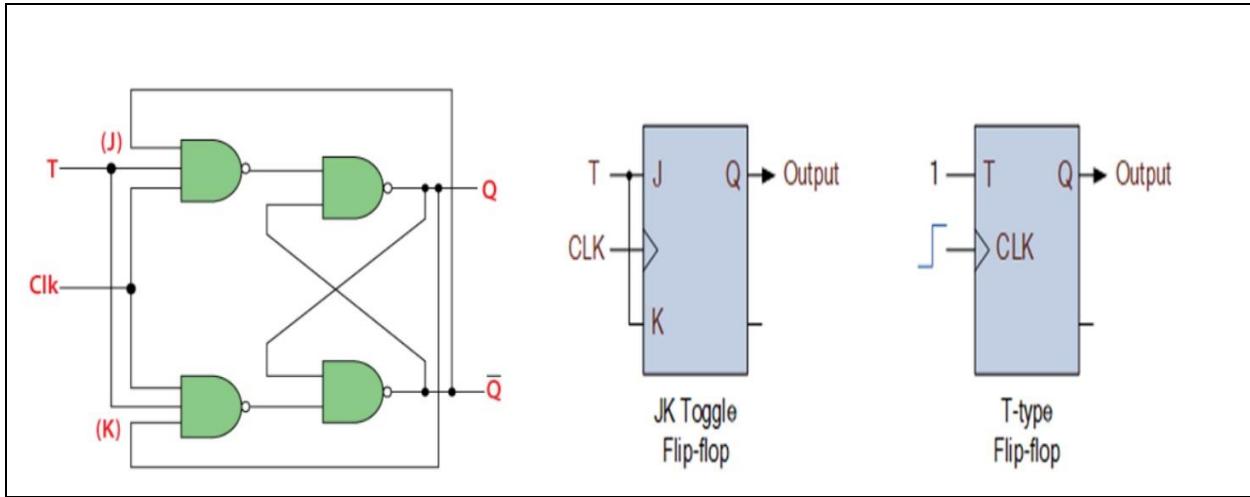

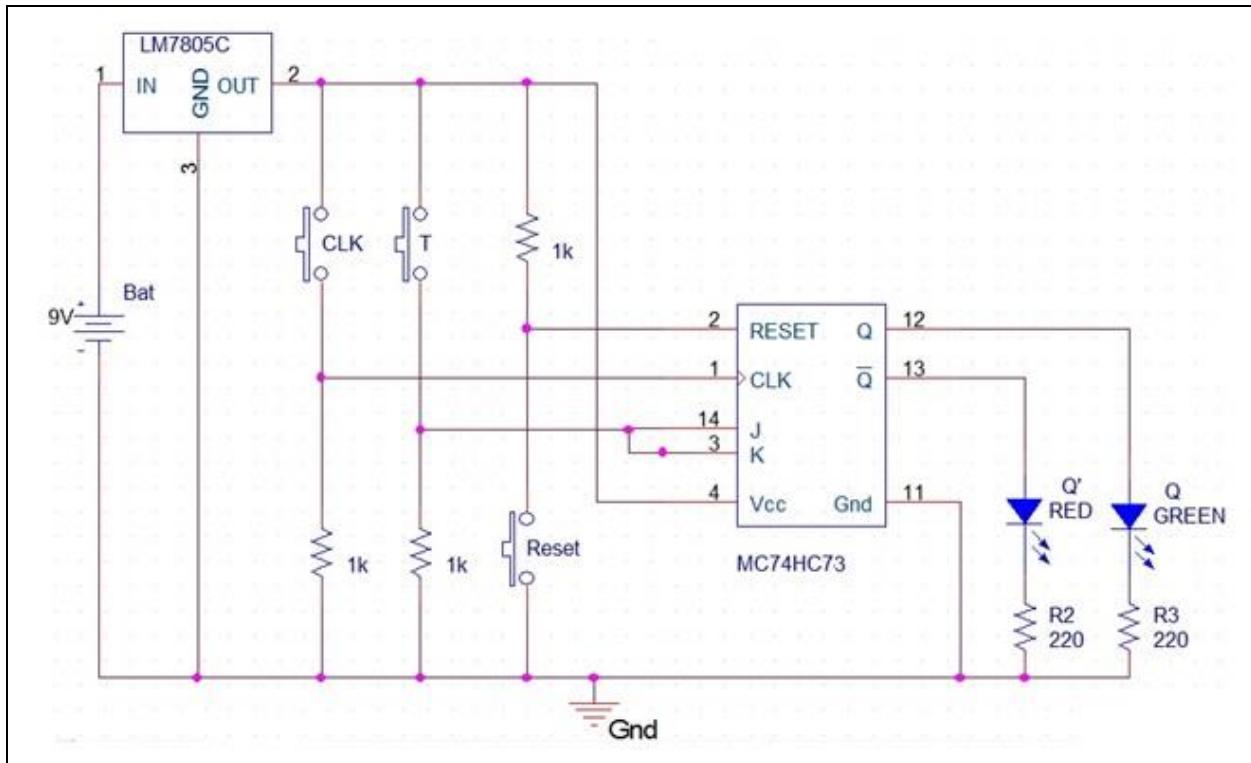

| 8.    | 38 - 44  |      | P3                | 3   | To OPERATE UNDER SUPERVISION JK Flip Flop and T-Flip Flop.                                                                                              |       |

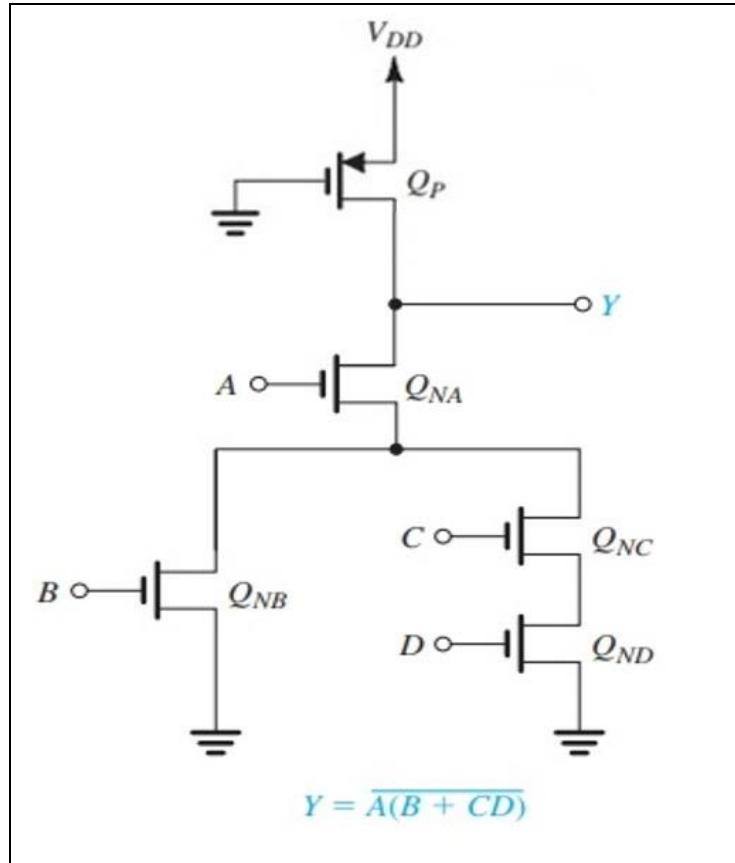

| 9.    | 45 - 48  |      | P3                | 3   | To OPERATE UNDER SUPERVISION the Pseudo NMOS Logic inverter and TRY complex logic function $f = \overline{A(B + CD)}$ .                                 |       |

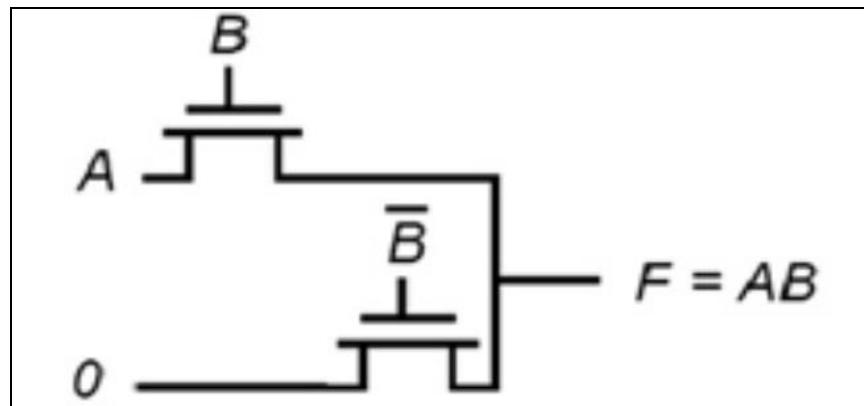

| 10.   | 49 - 54  |      | P3                | 3   | To OPERATE UNDER SUPERVISION pass transistor logic to implement two input AND gate and PRACTICE 2-to-1 multiplexer using CMOS transmission gates.       |       |

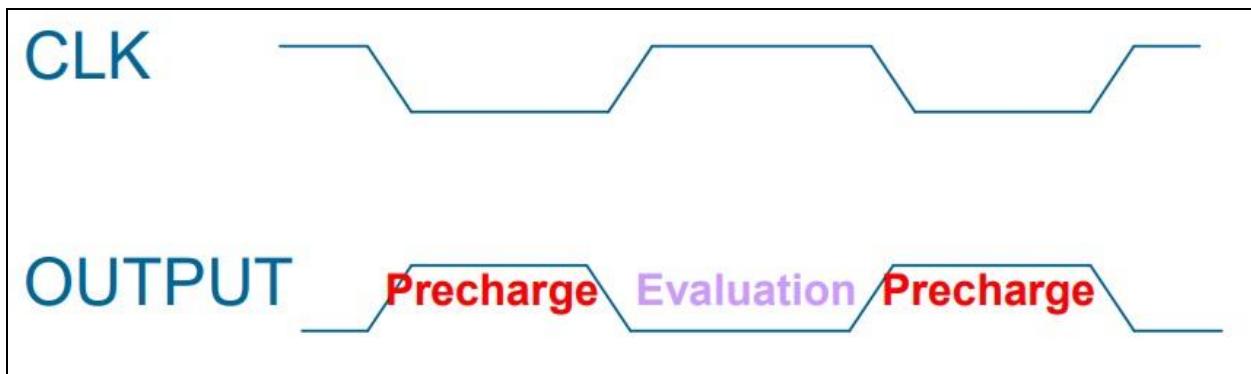

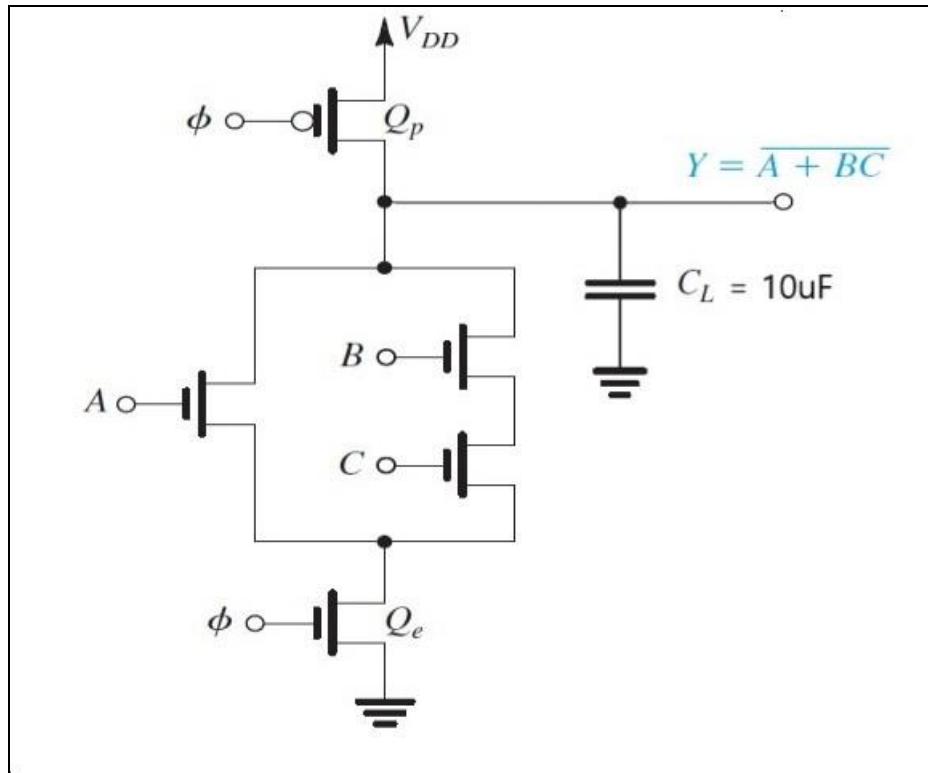

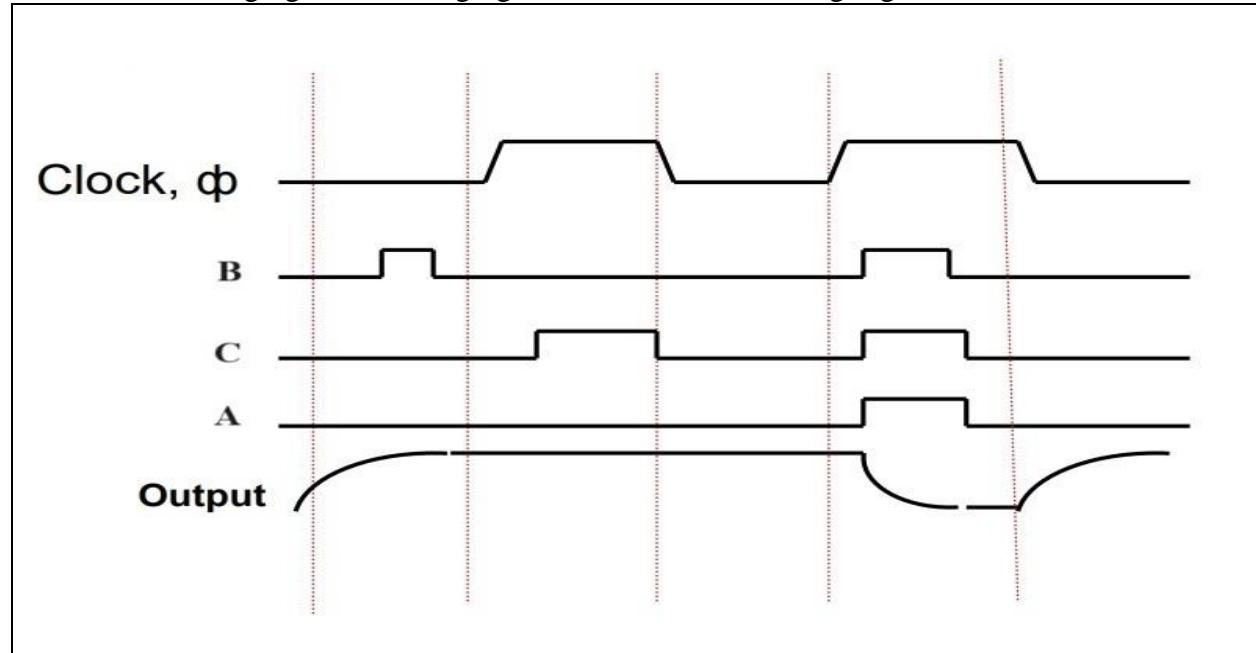

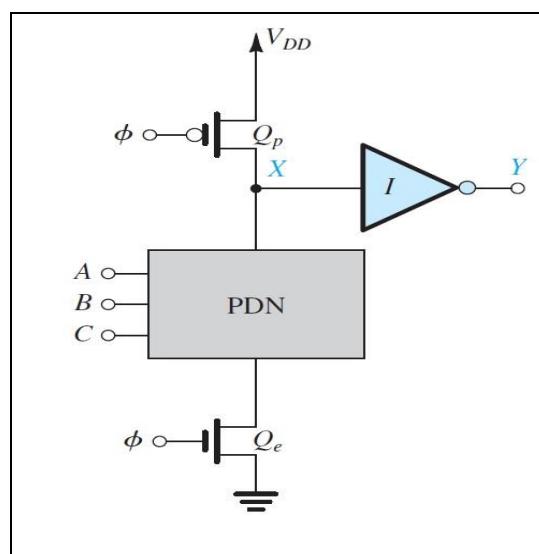

| 11.   | 55 - 59  |      | P3                | 3   | To OPERATE UNDER SUPERVISION the Dynamic logic circuit and PRACTICE the function $Y = \overline{A + BC}$ .                                              |       |

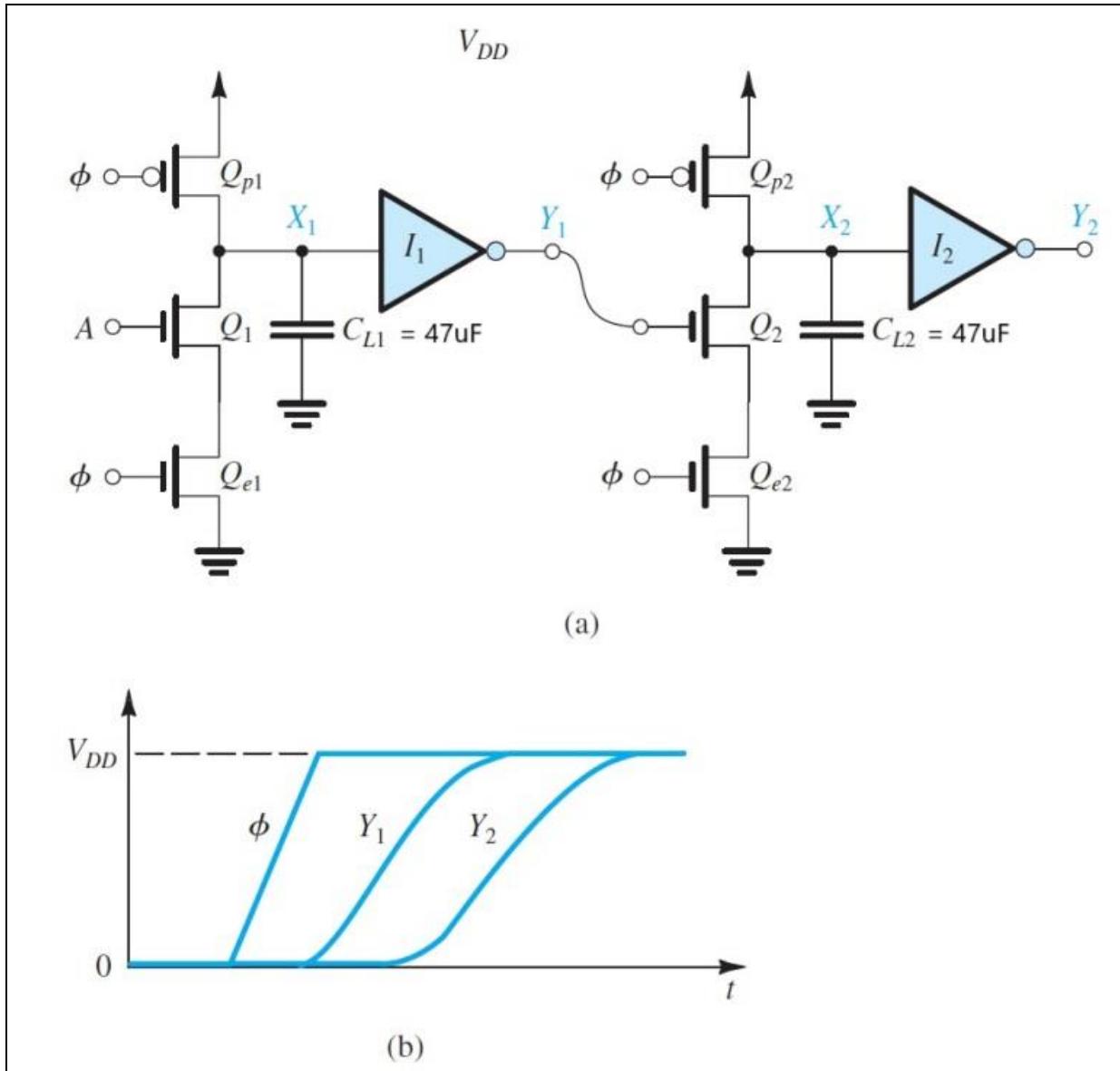

| 12.   | 60 - 63  |      | P3                | 3   | To OPERATE UNDER SUPERVISION two single-input Domino CMOS logic gates connected in cascade.                                                             |       |

| 13.   | 64 - 67  |      | P3                | 3   | Open Ended Lab                                                                                                                                          |       |

| S.No. | List of Experiments                                                                                                                                     | Weighted CLO | Sign. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|

| 1.    | To OPERATE UNDER SUPERVISION the CMOS op-amp to determine CMRR.                                                                                         |              |       |

| 2.    | To PRACTICE NMOS Inverter circuit with resistive load and determine the noise margin with the help of its voltage transfer characteristics.             |              |       |

| 3.    | To OPERATE UNDER SUPERVISION the NMOS Inverter to determine its average power dissipation and TRY NMOS NAND gate and NMOS NOR gate with resistive load. |              |       |

| 4.    | To PRACTICE NMOS Inverter circuit with Enhancement load MOS and TRY the logic function $f = \overline{(a + b)c}$ .                                      |              |       |

| 5.    | To OPERATE UNDER SUPERVISION the CMOS Inverter circuit and determine its propagation delay and power dissipation.                                       |              |       |

| 6.    | To PRACTICE CMOS NAND gate and CMOS NOR gate and also TRY exclusive OR-gate (XOR) function.                                                             |              |       |

| 7.    | To OPERATE UNDER SUPERVISION SR Flip Flop and D-Flip Flop.                                                                                              |              |       |

| 8.    | To OPERATE UNDER SUPERVISION JK Flip Flop and T-Flip Flop.                                                                                              |              |       |

| 9.    | To OPERATE UNDER SUPERVISION the Pseudo NMOS Logic inverter and TRY complex logic function $f = A(\overline{B} + \overline{C}D)$ .                      |              |       |

| 10.   | To OPERATE UNDER SUPERVISION pass transistor logic to implement two input AND gate and PRACTICE 2-to-1 multiplexer using CMOS transmission gates.       |              |       |

| 11.   | To OPERATE UNDER SUPERVISION the Dynamic logic circuit and PRACTICE the function $Y = \overline{A} + BC$ .                                              |              |       |

| 12.   | To OPERATE UNDER SUPERVISION two single-input Domino CMOS logic gates connected in cascade.                                                             |              |       |

| 13.   | Open Ended Lab                                                                                                                                          |              |       |

# LAB SESSION 01

## OBJECTIVE:

To OPERATE UNDER SUPERVISION the CMOS op-amp to determine CMRR.

## EQUIPMENT REQUIRED:

- Protoboard

- Function Generator

- Digital Multimeter

- Oscilloscope

- Op-amp IC MCP601/MCP602 : 2

- Resistors: 1K and 10K

## THEORY:

The Common-Mode Rejection Ratio (CMRR) indicates the ability of a differential amplifier to suppress signals common to the two inputs. It means that any undesired (or noise) signals that appear in polarity, or common to both input terminals, will be largely rejected, or cancelled out at the differential amplifier output. It is the ratio of the differential voltage gain ( $A_d$ ) to the common-mode gain ( $A_{cm}$ ). This ratio is the CMRR.

$$CMRR = \frac{A_d}{A_{cm}}$$

A well-designed differential amplifier typically has a high differential gain and low common mode gain, resulting in a high CMRR. The CMRR is often expressed in decibels (dB) as:

$$CMRR = 20 \log \left( \frac{A_d}{A_{cm}} \right)$$

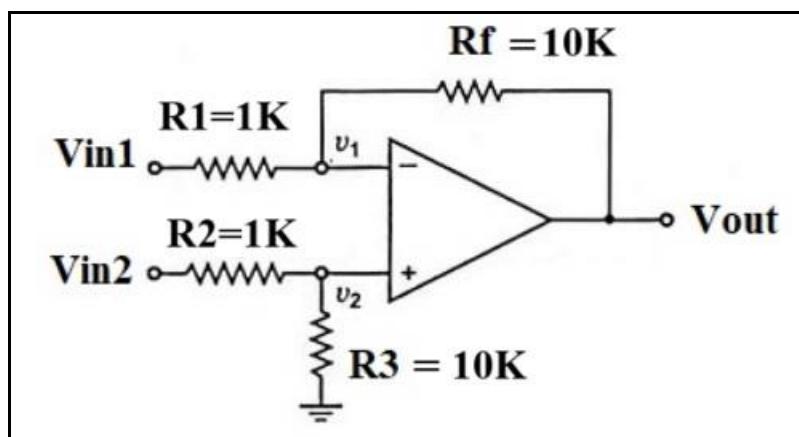

Figure 1: A CMOS op-amp circuit diagram

**Figure 2: (a) Circuit configurations for CMRR calculation (a) differential gain ( $A_d$ ) measurement and (b) common-mode gain ( $A_c$ ) measurement**

### **PROCEDURE:**

1. Assemble the op-amp shown in Figure 1 on the breadboard. Provide  $+\text{-}5\text{V}$  to the op-amp.

2. Connect one of the op-amp inputs to a function generator and ground the other input as shown in Figure 2(a) and find the differential gain ( $A_d$ ) of the op-amp.

3. Connect the op-amp in common mode configuration providing or shorting both op-amp inputs to a signal generator as shown in Figure 2(b) and find the common-mode gain ( $A_c$ ) of the op-amp.

4. Note down the observed values in the given Table 1.

5. Calculate the CMRR.

### **OBSERVATIONS:**

**Table 1: For CMRR of CMOS op-amp**

| <b>Quantity</b> | <b>Observed value</b> |

|-----------------|-----------------------|

| $A_d$           |                       |

| $A_{cm}$        |                       |

| CMRR            |                       |

## **CALCULATIONS:**

## **RESULTS:**

Differential gain of CMOS op-amp is: \_\_\_\_\_

Common mode gain of CMOS op-amp is: \_\_\_\_\_

CMRR of CMOS op-amp is: \_\_\_\_\_

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

Course Code and Title: EL-202 Integrated Circuits

| Psychomotor Domain Assessment Rubric-Level P3                                                                                              |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                 | Extent of Achievement                                                                            |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|                                                                                                                                            | 0                                                                                                | 1                                                                                                     | 2                                                                                                     | 3                                                                                                       | 4                                                                                                  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i> equipment and/or its component for a lab work.                         | Not able to identify the equipment.                                                              | --                                                                                                    | --                                                                                                    | --                                                                                                      | Able to identify equipment as well as its components.                                              |

| <b>Equipment Use</b><br>Sensory skills to <i>demonstrate</i> the use of the equipment for the lab work.                                    | Doesn't demonstrate the use of equipment.                                                        | Slightly demonstrates the use of equipment.                                                           | Somewhat demonstrates the use of equipment.                                                           | Moderately demonstrates the use of equipment.                                                           | Fully demonstrates the use of equipment.                                                           |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon sequence of steps in lab work.                                              | Not able to either learn or perform lab work procedure.                                          | Able to slightly understand lab work procedure and perform lab work.                                  | Able to somewhat understand lab work procedure and perform lab work.                                  | Able to moderately understand lab work procedure and perform lab work.                                  | Able to fully understand lab work procedure and perform lab work.                                  |

| <b>Response</b><br>Ability to <i>imitate</i> the lab work on his/her own.                                                                  | Not able to imitate the lab work.                                                                | Able to slightly imitate the lab work.                                                                | Able to somewhat imitate the lab work.                                                                | Able to moderately imitate the lab work.                                                                | Able to fully imitate the lab work.                                                                |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the observations from lab work for experimental verifications and illustrations. | Not able to use the observations from lab work for experimental verifications and illustrations. | Slightly able to use the observations from lab work for experimental verifications and illustrations. | Somewhat able to use the observations from lab work for experimental verifications and illustrations. | Moderately able to use the observations from lab work for experimental verifications and illustrations. | Fully able to use the observations from lab work for experimental verifications and illustrations. |

| <b>Safety Adherence</b><br>Adherence to <i>safety</i> procedures.                                                                          | Doesn't adhere to safety procedures.                                                             | Slightly adheres to safety procedures.                                                                | Somewhat adheres to safety procedures.                                                                | Moderately adheres to safety procedures.                                                                | Fully adheres to safety procedures.                                                                |

| <b>Equipment Handling</b><br><i>Equipment care</i> during the use.                                                                         | Doesn't handle equipment with required care.                                                     | Rarely handles equipment with required care.                                                          | Occasionally handles equipment with required care.                                                    | Often handles equipment with required care.                                                             | Handles equipment with required care.                                                              |

| <b>Group Work</b><br><i>Contributes</i> in a group based lab work.                                                                         | Doesn't participate and contribute.                                                              | Slightly participates and contributes.                                                                | Somewhat participates and contributes.                                                                | Moderately participates and contributes.                                                                | Fully participates and contributes.                                                                |

Laboratory Session No. \_\_\_\_\_

Date: \_\_\_\_\_

|                                   |  |

|-----------------------------------|--|

| Weighted CLO (Psychomotor Score)  |  |

| Remarks                           |  |

| Instructor's Signature with Date: |  |

## LAB SESSION 02

### **OBJECTIVE:**

To PRACTICE NMOS Inverter circuit with resistive load and determine the noise margin with the help of its voltage transfer characteristics.

### **EQUIPMENT REQUIRED:**

- Protoboard

- Variable Power Supply

- Digital Multimeter

- NMOS transistors 2N7000: 1

- Resistors: 1K

- LED

### **THEORY:**

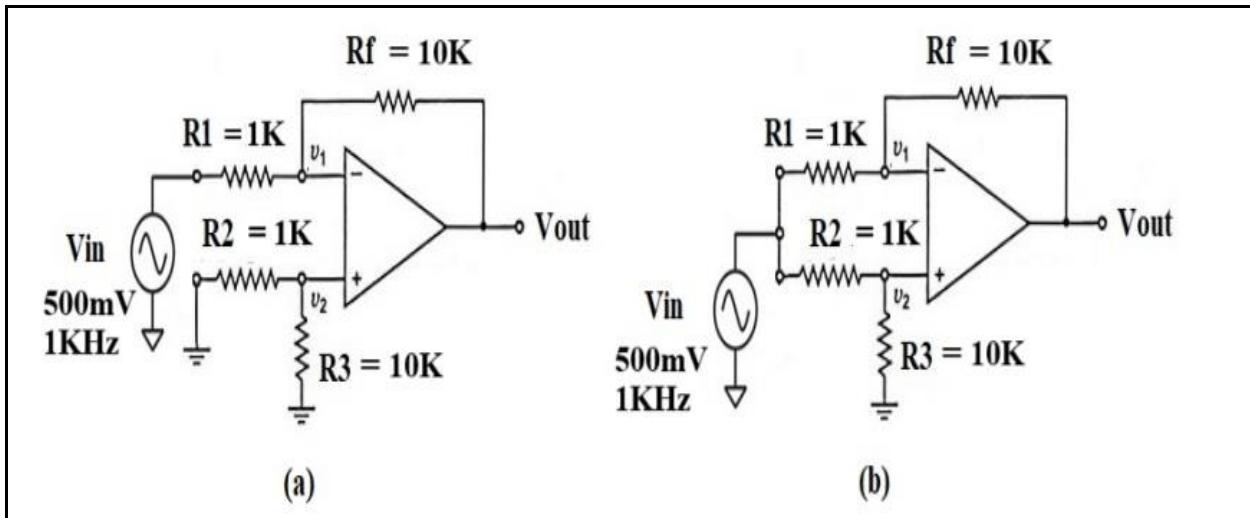

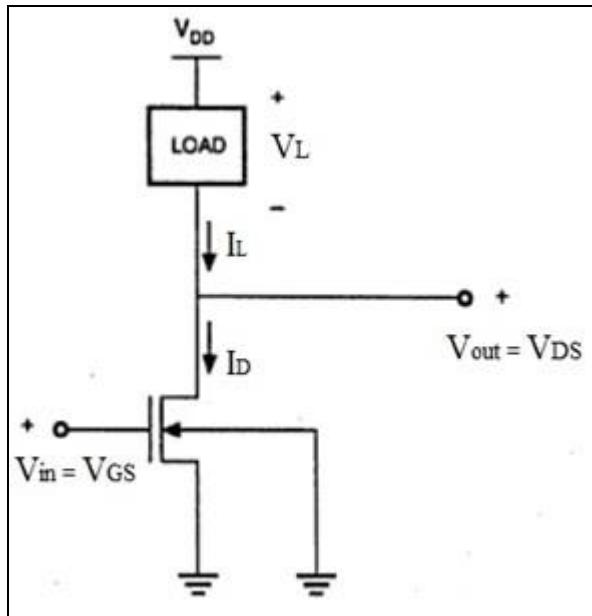

The basic transistor level realization of an inverter using an N-channel MOS transistor and a resistor is shown in the Figure 1. Here, enhancement type NMOS acts as the driver transistor. The load consists of a simple linear resistor  $R_L$ . The power supply of the circuit is  $V_{DD}$ .

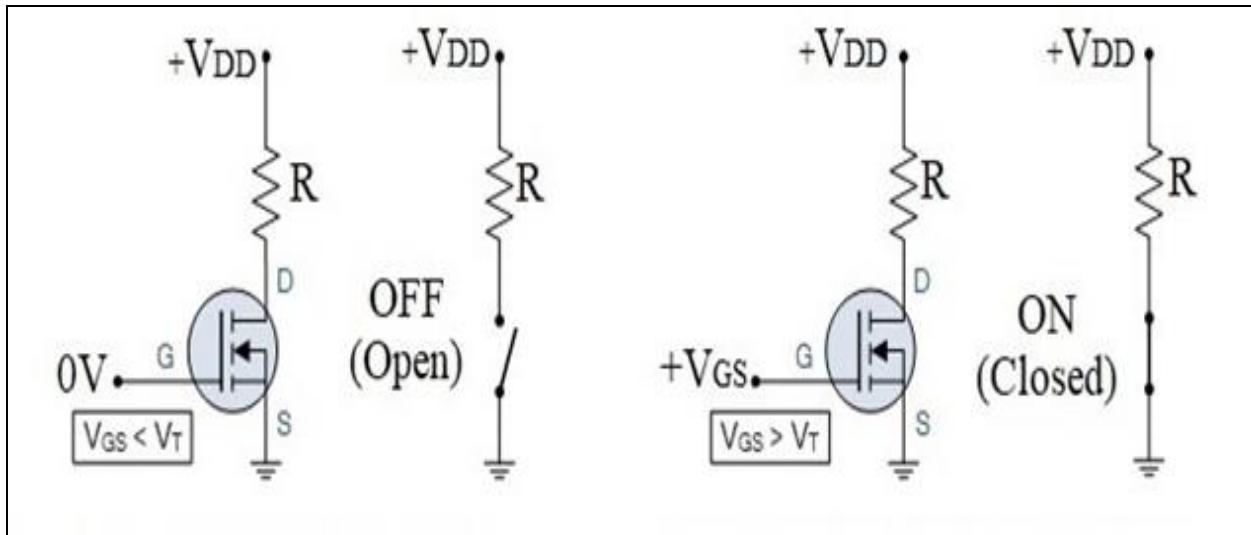

When the transistor is used as an inverter, the transistor is either cut-off and has a large voltage between its drain and source, or operates in triode region where its drain to source voltage is very small.

**Figure 1: NMOS Inverter**

When the input of the driver transistor is less than threshold voltage  $V_{TH}$  ( $V_{in} < V_{TH}$ ), driver transistor is in the cut – off region and does not conduct any current. So, the voltage drop across the load resistor is ZERO and output voltage is equal to the  $V_{DD}$ . The transistor is equivalent to

an open switch. Similarly, when input of the driver transistor is greater than the threshold voltage  $V_{TH}$  ( $V_{in} > V_{TH}$ ), the transistor is ON and connects the drain to source which is equivalent to a close switch and pulls the output voltage down to 0V.

Figure 2: (a) NMOS biased OFF (b) NMOS biased ON

### Noise Margin:

Noise margin is the amount of noise that a NMOS circuit could withstand without compromising the operation of circuit. It essentially represents the inverter's robustness against noise. Noise margin is typically divided into low noise margin (NML) and high noise margin (NMH).

### NML (Low Noise Margin):

NML is defined as the difference between the maximum low input voltage (VIL) recognized by the receiving gate and the maximum low output voltage (VOL) produced by the driving gate. A larger NML means the inverter is more tolerant to noise when the output is intended to be low.

The low-side noise margin is:

$$NML = VIL - VOL$$

### NMH (High Noise Margin):

NMH is defined as the difference between the minimum high output voltage (VOH) of the driving gate and the minimum high input voltage (VIH) recognized by the receiving gate. A larger NMH means the inverter is more tolerant to noise when the output is intended to be high.

The high-side noise margin is:

$$NMH = VOH - VIH$$

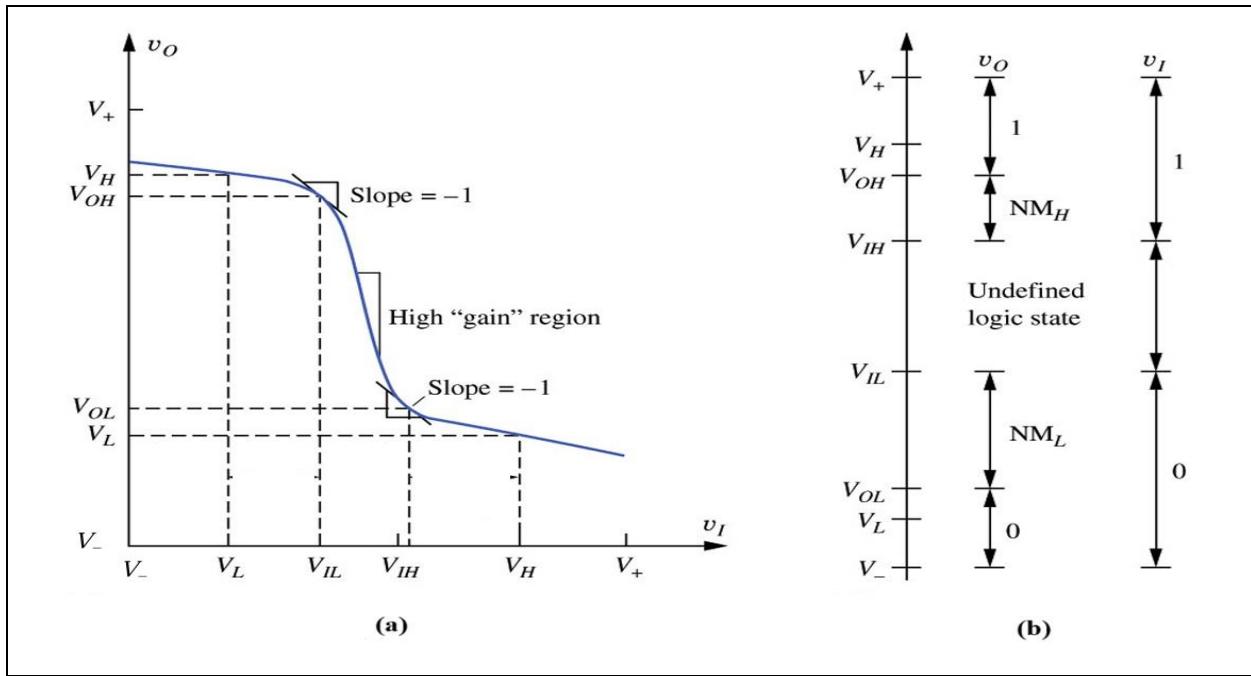

Figure 3 shows the voltage transfer characteristics (VTC) of the logic inverter, voltage levels, logic states and noise margins. Voltages between  $V_{IL}$  and  $V_{IH}$  are in the undefined range. If they are applied to a logic gate, the output cannot be predicted with certainty.

**Figure 3: (a) Voltage Transfer Characteristics of NMOS inverter (b) Voltage levels & Noise Margins**

The points, where the slope are -1, are important on the voltage transfer characteristics. These points specify the limits of the voltage ranges used to specify Logic 0 and logic 1.

### **PROCEDURE:**

1. Connect the circuit on breadboard according to the given Figure 1 for implementing NMOS inverter and note down the observed values in Table 1. Provide +5V to the circuit.

2. To observe the voltage transfer characteristics (VTC), vary the input voltage of NMOS inverter from 0V to 5V in 0.1V steps and measure the corresponding  $V_{out}$  with the help of digital multimeter (DMM).

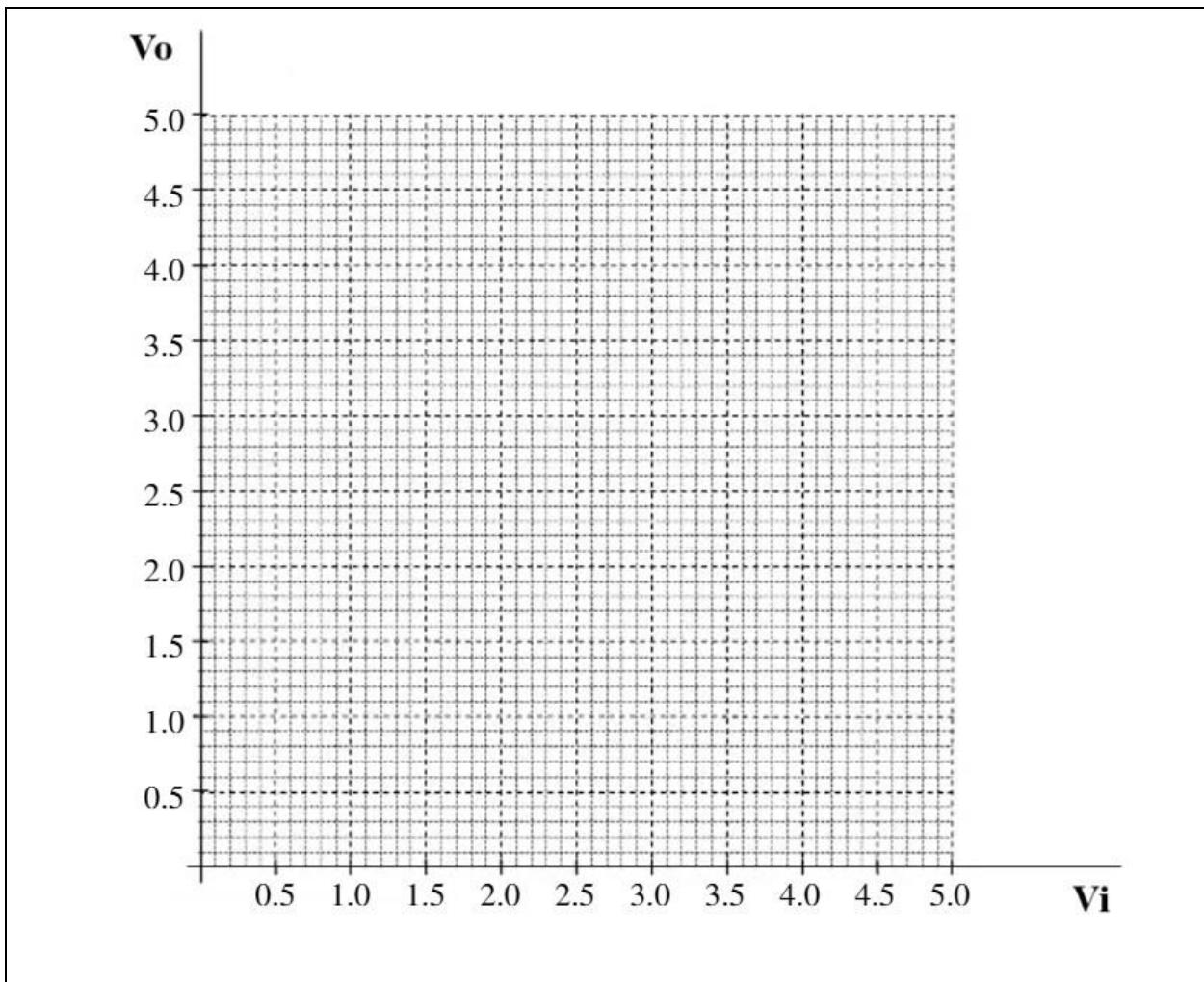

3. Note down the observed input ( $V_{in}$ ) and Output ( $V_{out}$ ) voltages in Table 2 and sketch the VTC in Figure 4.

4. Note down the values of  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$  and  $V_{OH}$  in Table 3.

5. Calculate the noise margin  $NM_H$  and  $NM_L$ .

**Table1: For NMOS Inverter**

| <b>Vin (Input)</b> | <b>Vout (Output)</b> |

|--------------------|----------------------|

| 0V                 |                      |

| 5V                 |                      |

**Table 2: For Voltage Transfer Characteristics (VTC)**

| <b>Input Voltage (Vin)</b> | <b>Output Voltage (Vout)</b> | <b>Input Voltage (Vin)</b> | <b>Output Voltage (Vout)</b> | <b>Input Voltage (Vin)</b> | <b>Output Voltage (Vout)</b> |

|----------------------------|------------------------------|----------------------------|------------------------------|----------------------------|------------------------------|

| 0                          |                              | 1.7                        |                              | 3.4                        |                              |

| 0.1                        |                              | 1.8                        |                              | 3.5                        |                              |

| 0.2                        |                              | 1.9                        |                              | 3.6                        |                              |

| 0.3                        |                              | 2                          |                              | 3.7                        |                              |

| 0.4                        |                              | 2.1                        |                              | 3.8                        |                              |

| 0.5                        |                              | 2.2                        |                              | 3.9                        |                              |

| 0.6                        |                              | 2.3                        |                              | 4                          |                              |

| 0.7                        |                              | 2.4                        |                              | 4.1                        |                              |

| 0.8                        |                              | 2.5                        |                              | 4.2                        |                              |

| 0.9                        |                              | 2.6                        |                              | 4.3                        |                              |

| 1                          |                              | 2.7                        |                              | 4.4                        |                              |

| 1.1                        |                              | 2.8                        |                              | 4.5                        |                              |

| 1.2                        |                              | 2.9                        |                              | 4.6                        |                              |

| 1.3                        |                              | 3                          |                              | 4.7                        |                              |

| 1.4                        |                              | 3.1                        |                              | 4.8                        |                              |

| 1.5                        |                              | 3.2                        |                              | 4.9                        |                              |

| 1.6                        |                              | 3.3                        |                              | 5                          |                              |

**Table 3: For Noise Margin**

| <b>Voltage Levels</b> | <b>Observed values</b> |

|-----------------------|------------------------|

| VIL                   |                        |

| VOL                   |                        |

| VIH                   |                        |

| VOH                   |                        |

| NML                   |                        |

| NMH                   |                        |

Figure 4: Voltage Transfer Characteristics of NMOS inverter

### CALCULATIONS:

### RESULTS:

Noise Margin low of NMOS (NML) inverter is: \_\_\_\_\_

Noise Margin high of NMOS (NMH) inverter is: \_\_\_\_\_

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

Course Code and Title: EL-202 Integrated Circuits

| Psychomotor Domain Assessment Rubric-Level P3                                                                                              |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                 | Extent of Achievement                                                                            |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|                                                                                                                                            | 0                                                                                                | 1                                                                                                     | 2                                                                                                     | 3                                                                                                       | 4                                                                                                  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i> equipment and/or its component for a lab work.                         | Not able to identify the equipment.                                                              | --                                                                                                    | --                                                                                                    | --                                                                                                      | Able to identify equipment as well as its components.                                              |

| <b>Equipment Use</b><br>Sensory skills to <i>demonstrate</i> the use of the equipment for the lab work.                                    | Doesn't demonstrate the use of equipment.                                                        | Slightly demonstrates the use of equipment.                                                           | Somewhat demonstrates the use of equipment.                                                           | Moderately demonstrates the use of equipment.                                                           | Fully demonstrates the use of equipment.                                                           |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon sequence of steps in lab work.                                              | Not able to either learn or perform lab work procedure.                                          | Able to slightly understand lab work procedure and perform lab work.                                  | Able to somewhat understand lab work procedure and perform lab work.                                  | Able to moderately understand lab work procedure and perform lab work.                                  | Able to fully understand lab work procedure and perform lab work.                                  |

| <b>Response</b><br>Ability to <i>imitate</i> the lab work on his/her own.                                                                  | Not able to imitate the lab work.                                                                | Able to slightly imitate the lab work.                                                                | Able to somewhat imitate the lab work.                                                                | Able to moderately imitate the lab work.                                                                | Able to fully imitate the lab work.                                                                |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the observations from lab work for experimental verifications and illustrations. | Not able to use the observations from lab work for experimental verifications and illustrations. | Slightly able to use the observations from lab work for experimental verifications and illustrations. | Somewhat able to use the observations from lab work for experimental verifications and illustrations. | Moderately able to use the observations from lab work for experimental verifications and illustrations. | Fully able to use the observations from lab work for experimental verifications and illustrations. |

| <b>Safety Adherence</b><br>Adherence to <i>safety</i> procedures.                                                                          | Doesn't adhere to safety procedures.                                                             | Slightly adheres to safety procedures.                                                                | Somewhat adheres to safety procedures.                                                                | Moderately adheres to safety procedures.                                                                | Fully adheres to safety procedures.                                                                |

| <b>Equipment Handling</b><br><i>Equipment care</i> during the use.                                                                         | Doesn't handle equipment with required care.                                                     | Rarely handles equipment with required care.                                                          | Occasionally handles equipment with required care.                                                    | Often handles equipment with required care.                                                             | Handles equipment with required care.                                                              |

| <b>Group Work</b><br><i>Contributes</i> in a group based lab work.                                                                         | Doesn't participate and contribute.                                                              | Slightly participates and contributes.                                                                | Somewhat participates and contributes.                                                                | Moderately participates and contributes.                                                                | Fully participates and contributes.                                                                |

Laboratory Session No. \_\_\_\_\_

Date: \_\_\_\_\_

|                                   |  |

|-----------------------------------|--|

| Weighted CLO (Psychomotor Score)  |  |

| Remarks                           |  |

| Instructor's Signature with Date: |  |

## LAB SESSION 03

### OBJECTIVE:

To OPERATE UNDER SUPERVISION the NMOS Inverter to determine its average power dissipation and TRY NMOS NAND gate and NMOS NOR gate with resistive load.

### EQUIPMENT REQUIRED:

- Protoboard

- Variable Power Supply

- Digital Multimeter

- NMOS transistors 2N7000: 5

- Resistors: 1K

- LED

### THEORY:

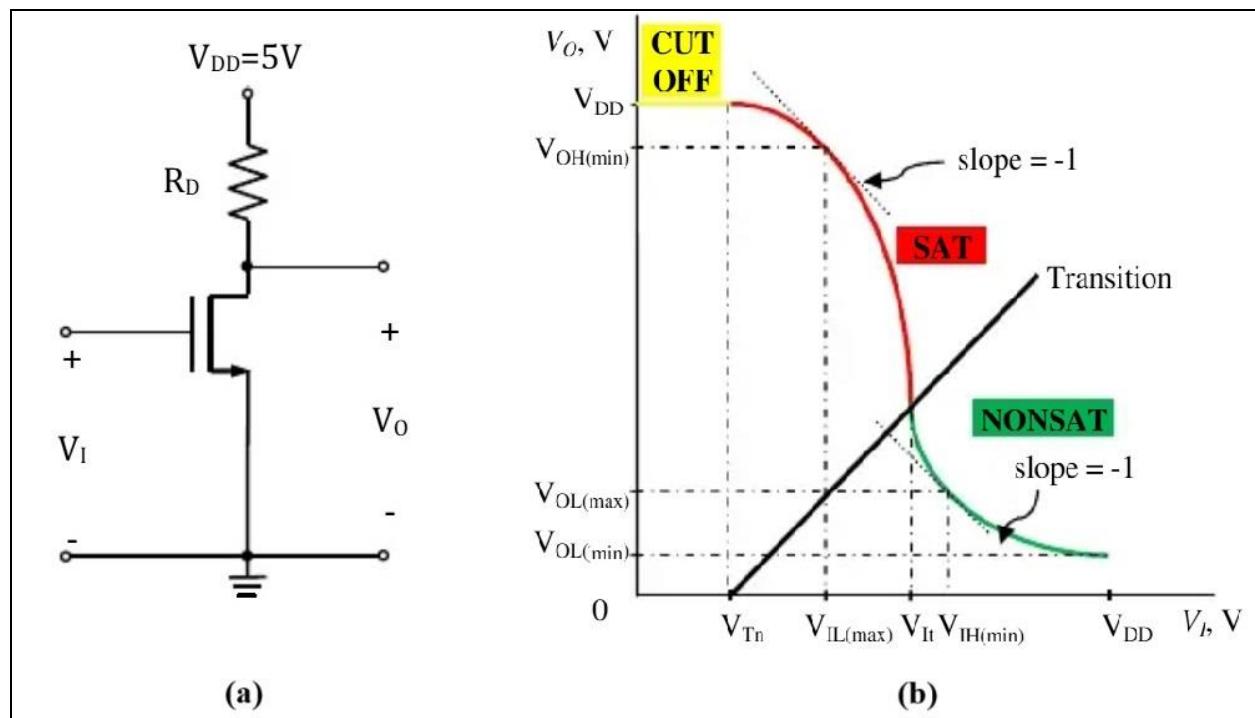

An NMOS inverter with resistive load and its voltage transfer characteristics are shown in Figure 1(a) and Figure 1(b) respectively.

**Figure 1: (a) NMOS inverter with resistive load (b) Voltage Transfer Characteristics of NMOS inverter**

The average power dissipated in the NMOS logic gate is calculated assuming half of the period, input is high (output is low) and during the other half input is low (output is high). When the

output is high ( $V_{in} = 0$  V), the output current is zero,  $I_{D(OH)} = 0$  V, since the transistor is off. For  $V_{in} = 5$  V, the output is low ( $V_{OL(min)}$  as shown in the above characteristic curve) and the current through it is:

$$I_{D(OL)} = \frac{V_{DD} - V_{OL}}{R_D}$$

Then the average current is:

$$I_{D(avg)} = \frac{I_{D(OL)} + I_{D(OH)}}{2}$$

and the average power dissipation is:

$$P_{D(avg)} = V_{DD} \cdot I_{D(avg)}$$

### **PROCEDURE:**

1. Connect the circuit on breadboard according to the given Figure 1(a) for implementing NMOS inverter with resistive load. Provide +5V to the circuit.

2. Apply a stable input (0/1) to the input of the NMOS inverter.

3. Use a Digital Multimeter (DMM) to find  $V_{OL}$  and calculate  $I_{D(OL)}$  and  $I_{D(avg)}$ .

4. Calculate the average power dissipation ( $P_{D(avg)}$ ) and note down the value in Table 1.

5. For implementing NAND gate, connect two transistors in series and note down the observed value in Table 2.

6. For implementing NOR gate, connect two transistors in parallel and note down the observed value in Table 2.

### **OBSERVATIONS:**

**Table 1: For Average Power Dissipation of NMOS Inverter**

| Average Current and Power | Observed Values |

|---------------------------|-----------------|

| $I_{D(avg)}$              |                 |

| $P_{D(avg)}$              |                 |

**Table 2: For NAND and NOR gate**

| NAND GATE |    | NOR GATE |      |    |

|-----------|----|----------|------|----|

| Vin       |    | Vout     | Vout |    |

| 0V        | 0V |          | 0V   | 0V |

| 5V        | 0V |          | 5V   | 0V |

| 0V        | 5V |          | 0V   | 5V |

| 5V        | 5V |          | 5V   | 5V |

## **CALCULATIONS:**

## **RESULTS:**

Average Power dissipation of NMOS inverter is: \_\_\_\_\_

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

Course Code and Title: EL-202 Integrated Circuits

| Psychomotor Domain Assessment Rubric-Level P3                                                                                              |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                 | Extent of Achievement                                                                            |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|                                                                                                                                            | 0                                                                                                | 1                                                                                                     | 2                                                                                                     | 3                                                                                                       | 4                                                                                                  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i> equipment and/or its component for a lab work.                         | Not able to identify the equipment.                                                              | --                                                                                                    | --                                                                                                    | --                                                                                                      | Able to identify equipment as well as its components.                                              |

| <b>Equipment Use</b><br>Sensory skills to <i>demonstrate</i> the use of the equipment for the lab work.                                    | Doesn't demonstrate the use of equipment.                                                        | Slightly demonstrates the use of equipment.                                                           | Somewhat demonstrates the use of equipment.                                                           | Moderately demonstrates the use of equipment.                                                           | Fully demonstrates the use of equipment.                                                           |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon sequence of steps in lab work.                                              | Not able to either learn or perform lab work procedure.                                          | Able to slightly understand lab work procedure and perform lab work.                                  | Able to somewhat understand lab work procedure and perform lab work.                                  | Able to moderately understand lab work procedure and perform lab work.                                  | Able to fully understand lab work procedure and perform lab work.                                  |

| <b>Response</b><br>Ability to <i>imitate</i> the lab work on his/her own.                                                                  | Not able to imitate the lab work.                                                                | Able to slightly imitate the lab work.                                                                | Able to somewhat imitate the lab work.                                                                | Able to moderately imitate the lab work.                                                                | Able to fully imitate the lab work.                                                                |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the observations from lab work for experimental verifications and illustrations. | Not able to use the observations from lab work for experimental verifications and illustrations. | Slightly able to use the observations from lab work for experimental verifications and illustrations. | Somewhat able to use the observations from lab work for experimental verifications and illustrations. | Moderately able to use the observations from lab work for experimental verifications and illustrations. | Fully able to use the observations from lab work for experimental verifications and illustrations. |

| <b>Safety Adherence</b><br>Adherence to <i>safety</i> procedures.                                                                          | Doesn't adhere to safety procedures.                                                             | Slightly adheres to safety procedures.                                                                | Somewhat adheres to safety procedures.                                                                | Moderately adheres to safety procedures.                                                                | Fully adheres to safety procedures.                                                                |

| <b>Equipment Handling</b><br><i>Equipment care</i> during the use.                                                                         | Doesn't handle equipment with required care.                                                     | Rarely handles equipment with required care.                                                          | Occasionally handles equipment with required care.                                                    | Often handles equipment with required care.                                                             | Handles equipment with required care.                                                              |

| <b>Group Work</b><br><i>Contributes</i> in a group based lab work.                                                                         | Doesn't participate and contribute.                                                              | Slightly participates and contributes.                                                                | Somewhat participates and contributes.                                                                | Moderately participates and contributes.                                                                | Fully participates and contributes.                                                                |

Laboratory Session No. \_\_\_\_\_

Date: \_\_\_\_\_

|                                   |  |

|-----------------------------------|--|

| Weighted CLO (Psychomotor Score)  |  |

| Remarks                           |  |

| Instructor's Signature with Date: |  |

## LAB SESSION 04

### OBJECTIVE:

To PRACTICE NMOS Inverter circuit with Enhancement load MOS and TRY the logic function  $f = \overline{(a + b)c}$ .

### EQUIPMENT REQUIRED:

- Protoboard

- Power Supply

- Digital Multimeter

- Oscilloscope

- NMOS transistors 2N7000: 6

- LED

### THEORY:

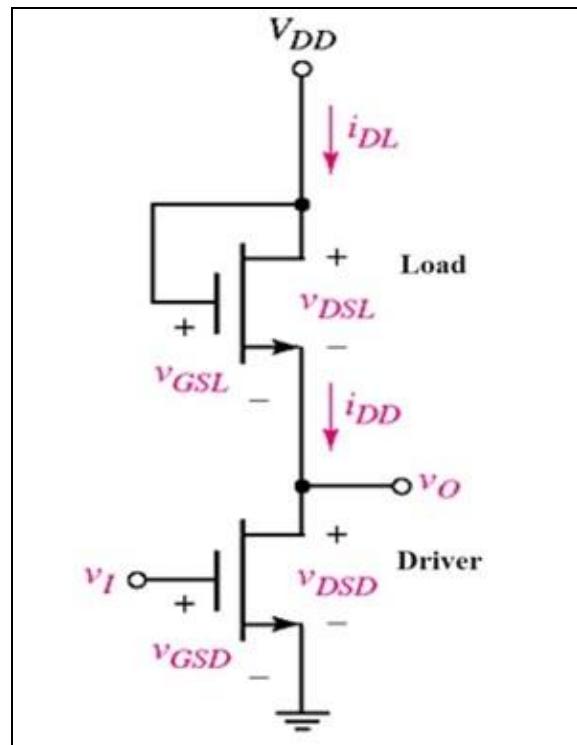

NMOS inverter using enhancement type NMOS transistor as load is shown in Figure 1. The NMOS load transistor is operated in saturation region. Its gate and drain are shorted together and connected to a supply voltage  $V_{DD}$ . When the input to the inverter is at logic low, the driver NMOS transistor is turned off and the output is at logic high through the load transistor. Conversely, when the input is at logic high, the driver NMOS transistor is turned on connecting the output to ground through the driver transistor.

Figure 1: NMOS Inverter with Enhancement load

NMOS transistor with resistive load offers an advantage over resistive loads in terms of area efficiency but it can result in significant static power dissipation.

### **PROCEDURE:**

1. For implementing NMOS inverter with Enhancement load MOS connect the circuit on breadboard according to the given Figure 1 and note down the observed values in Table 1. Provide +5V to the circuit.

2. For implementing the given logic function  $f = \overline{(a + b)c}$ , connect two transistors in parallel with input a and b.

3. Then connect a transistor with input c in series with the two parallel transistors having inputs a and b connected above.

4. Now note down the observed value in Table 2.

### **OBSERVATIONS:**

**Table 1: For NMOS Inverter with Enhancement Load MOS**

| <b>V<sub>in</sub></b> | <b>V<sub>out</sub></b> |

|-----------------------|------------------------|

| 0V                    |                        |

| 5V                    |                        |

**Table 2: For  $f = \overline{(a + b)c}$**

| <b><math>f = \overline{(a + b)c}</math></b> |                 |                 |                 |

|---------------------------------------------|-----------------|-----------------|-----------------|

| <b><i>a</i></b>                             | <b><i>b</i></b> | <b><i>c</i></b> | <b><i>f</i></b> |

|                                             |                 |                 |                 |

|                                             |                 |                 |                 |

|                                             |                 |                 |                 |

|                                             |                 |                 |                 |

|                                             |                 |                 |                 |

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

Course Code and Title: EL-202 Integrated Circuits

| Psychomotor Domain Assessment Rubric-Level P3                                                                                              |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                 | Extent of Achievement                                                                            |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|                                                                                                                                            | 0                                                                                                | 1                                                                                                     | 2                                                                                                     | 3                                                                                                       | 4                                                                                                  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i> equipment and/or its component for a lab work.                         | Not able to identify the equipment.                                                              | --                                                                                                    | --                                                                                                    | --                                                                                                      | Able to identify equipment as well as its components.                                              |

| <b>Equipment Use</b><br>Sensory skills to <i>demonstrate</i> the use of the equipment for the lab work.                                    | Doesn't demonstrate the use of equipment.                                                        | Slightly demonstrates the use of equipment.                                                           | Somewhat demonstrates the use of equipment.                                                           | Moderately demonstrates the use of equipment.                                                           | Fully demonstrates the use of equipment.                                                           |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon sequence of steps in lab work.                                              | Not able to either learn or perform lab work procedure.                                          | Able to slightly understand lab work procedure and perform lab work.                                  | Able to somewhat understand lab work procedure and perform lab work.                                  | Able to moderately understand lab work procedure and perform lab work.                                  | Able to fully understand lab work procedure and perform lab work.                                  |

| <b>Response</b><br>Ability to <i>imitate</i> the lab work on his/her own.                                                                  | Not able to imitate the lab work.                                                                | Able to slightly imitate the lab work.                                                                | Able to somewhat imitate the lab work.                                                                | Able to moderately imitate the lab work.                                                                | Able to fully imitate the lab work.                                                                |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the observations from lab work for experimental verifications and illustrations. | Not able to use the observations from lab work for experimental verifications and illustrations. | Slightly able to use the observations from lab work for experimental verifications and illustrations. | Somewhat able to use the observations from lab work for experimental verifications and illustrations. | Moderately able to use the observations from lab work for experimental verifications and illustrations. | Fully able to use the observations from lab work for experimental verifications and illustrations. |

| <b>Safety Adherence</b><br>Adherence to <i>safety</i> procedures.                                                                          | Doesn't adhere to safety procedures.                                                             | Slightly adheres to safety procedures.                                                                | Somewhat adheres to safety procedures.                                                                | Moderately adheres to safety procedures.                                                                | Fully adheres to safety procedures.                                                                |

| <b>Equipment Handling</b><br><i>Equipment care</i> during the use.                                                                         | Doesn't handle equipment with required care.                                                     | Rarely handles equipment with required care.                                                          | Occasionally handles equipment with required care.                                                    | Often handles equipment with required care.                                                             | Handles equipment with required care.                                                              |

| <b>Group Work</b><br><i>Contributes</i> in a group based lab work.                                                                         | Doesn't participate and contribute.                                                              | Slightly participates and contributes.                                                                | Somewhat participates and contributes.                                                                | Moderately participates and contributes.                                                                | Fully participates and contributes.                                                                |

Laboratory Session No. \_\_\_\_\_

Date: \_\_\_\_\_

|                                   |  |

|-----------------------------------|--|

| Weighted CLO (Psychomotor Score)  |  |

| Remarks                           |  |

| Instructor's Signature with Date: |  |

# LAB SESSION 05

## OBJECTIVE:

To OPERATE UNDER SUPERVISION the CMOS Inverter circuit and determine its propagation delay and power dissipation.

## EQUIPMENT REQUIRED:

- Protoboard

- Function Generator

- Oscilloscope

- Power Supply

- Digital Multimeter

- NMOS transistor 2N7000/IRF540 : 2

- PMOS transistor IRF9540 : 2

- Capacitor: 0.1uF and 1uF

## THEORY:

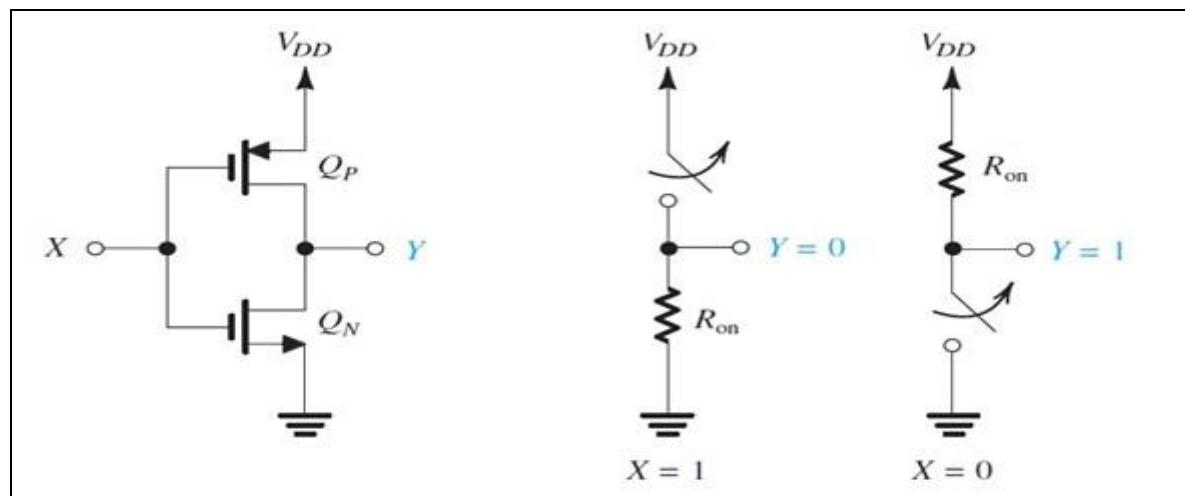

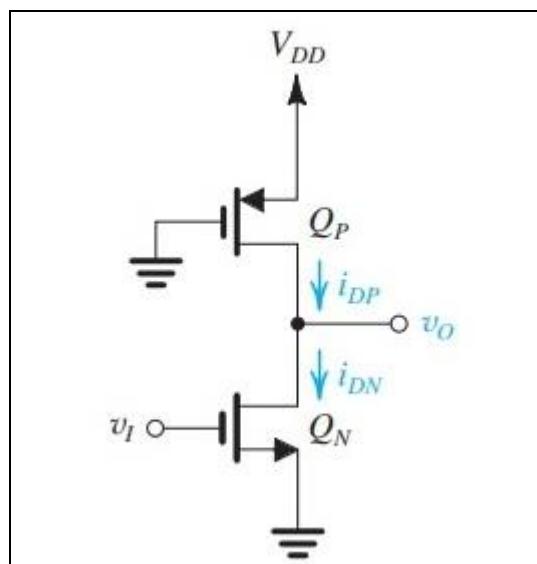

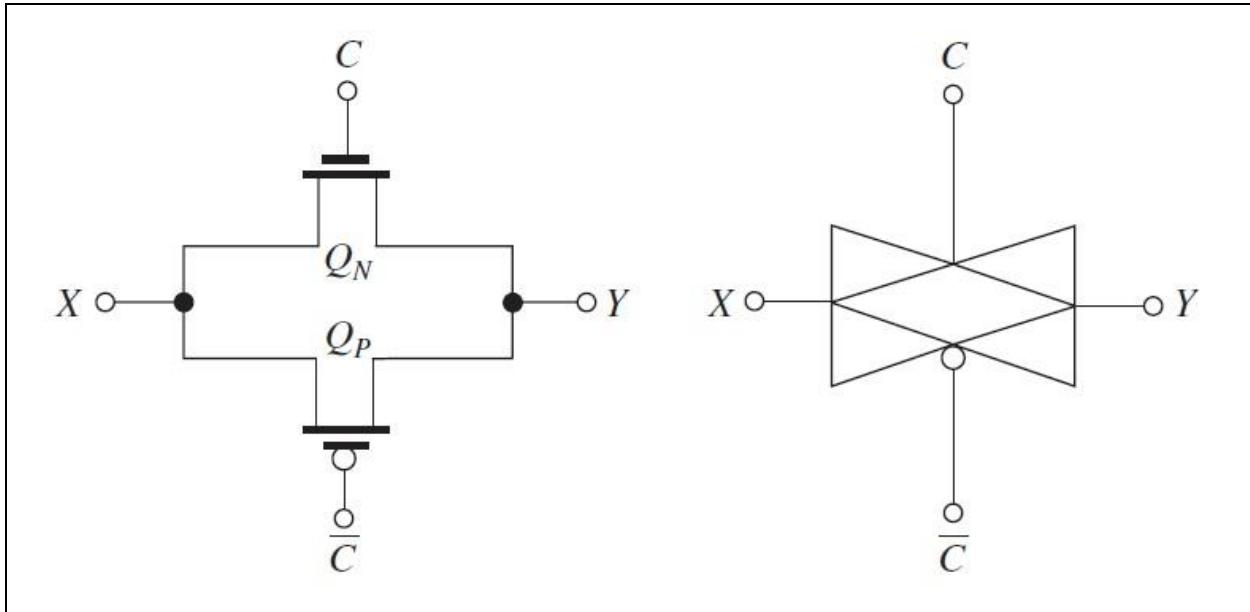

The CMOS circuit implementation is shown in Figure 1. It consists of an NMOS transistor  $QN$  and a PMOS transistor  $QP$ , with the gate terminals connected together to constitute the inverter input terminal, to which a logic input  $X$  is applied. Also, both drain terminals are connected together to constitute the inverter output terminal on which the output logic variable  $Y$  appears. When  $X = 1$  that is,  $VX = VDD$ , the PMOS transistor will be off but the NMOS transistor will be on and will be connecting the inverter output terminal to ground through the small on-resistance  $R_{on}$ . Thus, the output voltage will be zero and  $Y = 0$ . When  $X = 0$ , that is,  $VX = 0$ , as shown in Figure 1(b), the NMOS transistor will be off but the PMOS transistor will be on and will be connecting the output terminal to  $VDD$  through the small resistance  $R_{on}$ . Thus the output voltage will be equal to  $VDD$  and  $Y$  will be 1.

Figure 1: (a) CMOS inverter (b) Operation when input is at logic 1 and 0

## Propagation Delay:

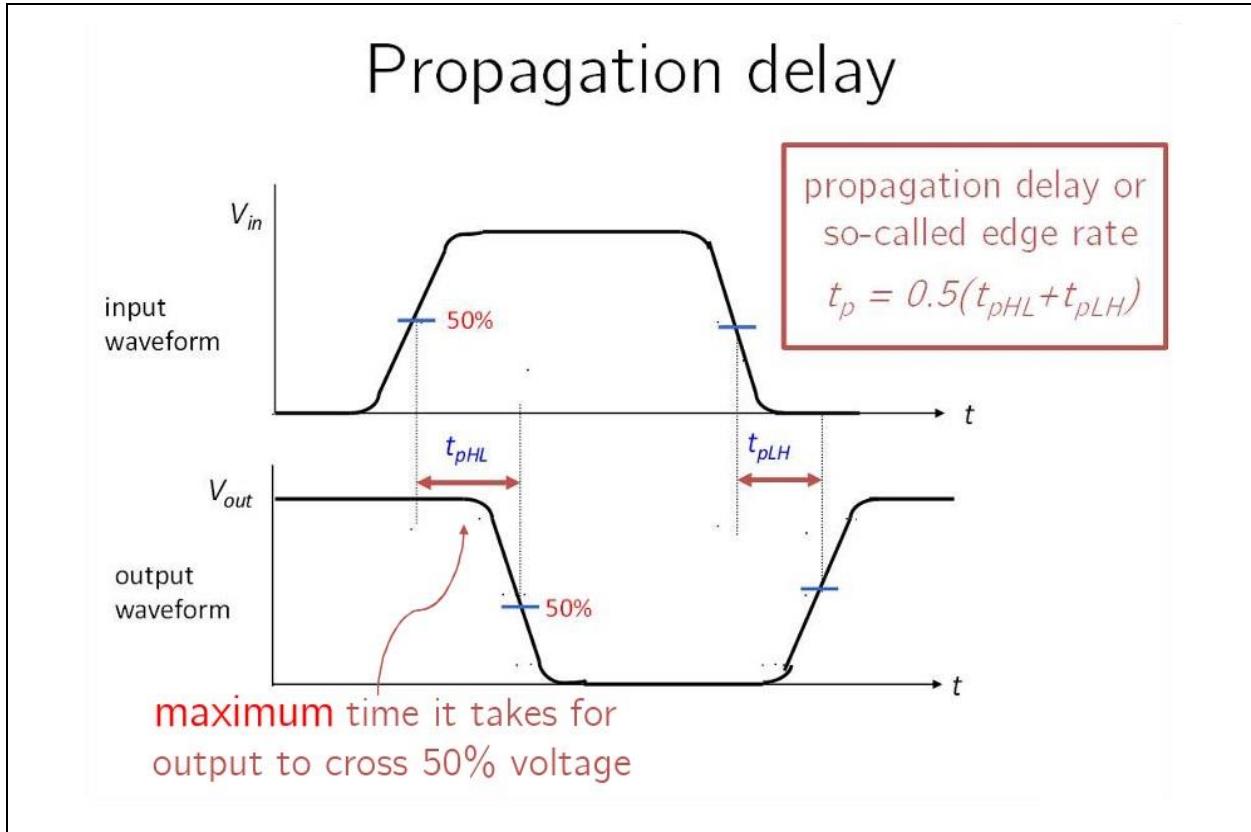

The propagation delay ( $t_p$ ) of a gate is defined as the time taken by a gate to respond when there is change at its inputs. It expresses the delay experienced by a signal when passing through a gate. It is measured between the **50%** transition points of the input and output waveforms as shown in Figure 2 for an inverter.

Figure 2: Propagation delay of CMOS Inverter

## Propagation Delay from High to Low (tpHL):

This delay is the time it takes for the output to respond when the input switches from high to low. More specifically, it measures how long it takes the output to fall to **50%** of its full value after the input starts changing. The smaller this delay, the faster the inverter reacts to a falling edge input.

### **Propagation Delay from Low to High (tpLH):**

This is similar to tpHL but in the opposite direction. It measures how long it takes for the output to rise to **50%** when the input goes from low to high. Again, shorter delay times mean the inverter can keep up with faster signal changes.

### **Total Propagation Delay (tp):**

The total propagation delay is found by taking the average of tpHL and tpLH which represents the overall delay of the inverter.

$$t_p = \frac{(tp_{HL} + tp_{LH})}{2}$$

This value gives you a good overall sense of how quickly the inverter reacts to any change, whether the input rises or falls.

### **Power Dissipation of CMOS Inverter:**

Power dissipation in CMOS circuits comes from two components:

- Static Power Dissipation

- Dynamic Power Dissipation

### **Static Power Dissipation:**

The power lost due to current leakage during which the circuit is dormant is referred to as a static power. This is caused by leakage currents, which are small currents flowing even when the transistors are in the cutoff region. Static power dissipation can be calculated as:

$$P_{\text{static}} = I \cdot V_{DD}$$

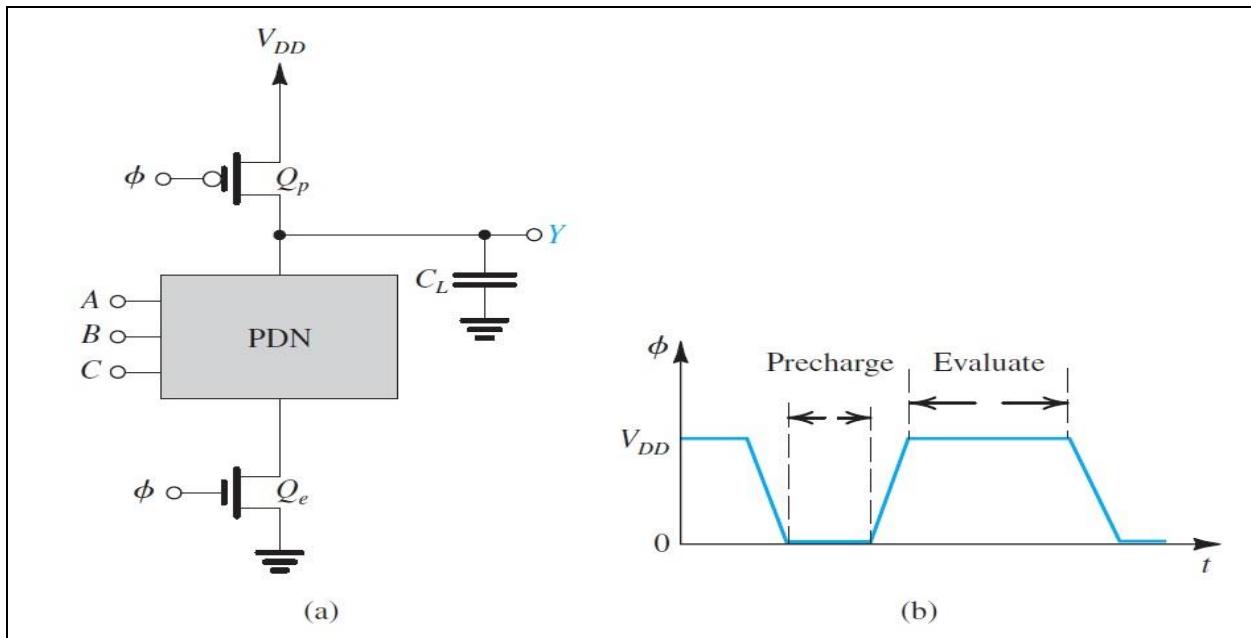

### **Dynamic Power Dissipation:**

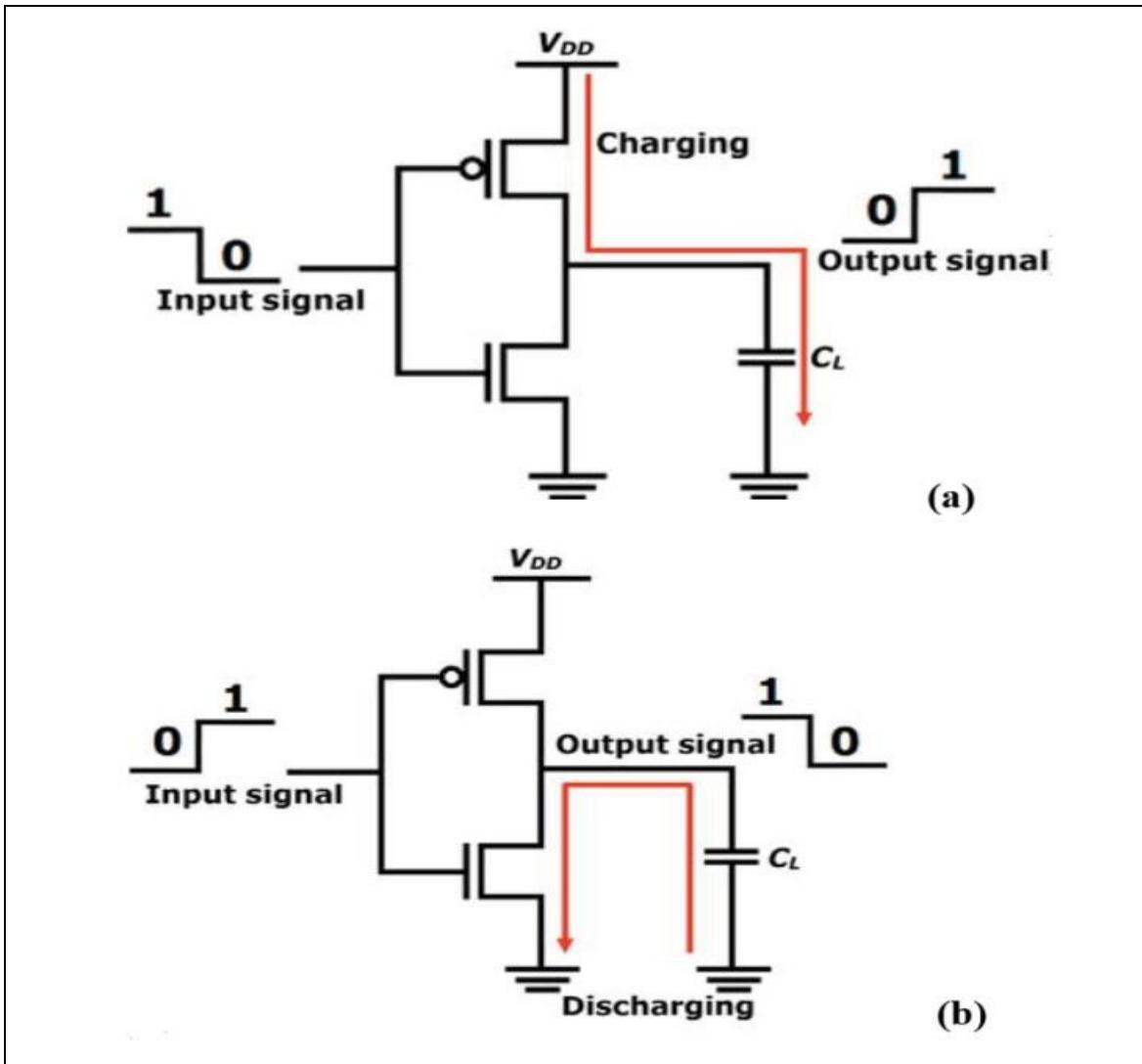

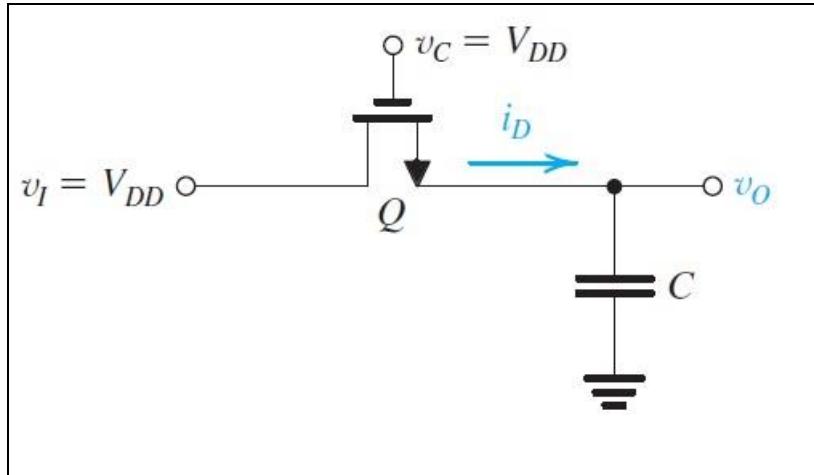

The power consumed by the circuit when it is performing computational task is known as dynamic power. This power dissipation occurs when the inverter switches, causing the load capacitance ( $C_L$ ) to charge and discharge as shown in Figure 3.

Figure 3: (a) Charging path ( $V_{DD}$  to  $C_L$ ) (b) Discharging path ( $C_L$  to GND) in CMOS circuit

Whenever the input signal of the circuit changes its state with time, it causes some power dissipation. Dynamic power is required to charging and discharging the load capacitance when transistor input switches. When the input switches from 1 to 0 the PMOS transistor (PULL UP network) turns ON and charges the load to  $V_{DD}$ . And that time energy stored in the capacitance is:

$$E_C = \frac{1}{2} C_L V_{DD}^2$$

The energy delivered from the power supply is:

$$E_C = C_L V_{DD}^2$$

Observed that only half of the energy from the power supply is stored in the capacitor. The other half is dissipated (converted to heat) in the PMOS transistor because transistor has a voltage across it at the same time current flows through it. The dissipated power depends on only the load capacitance not on transistor or speed at which the gate switches.

When the input switches from 0 to 1, the PMOS transistor turns off and the NMOS transistor is turned ON, and discharging the capacitor. The energy stored in the capacitor is dissipated in the NMOS transistor. No energy is drawn from the power supply in this case.

Depending upon the inputs at the gate of the transistor one gate is on the other is off because of charging and discharging of the capacitor. On rising edge output change  $Q = C_L V_{DD}$  is required to charge the output node to  $V_{DD}$  (i.e. cap is charged to  $V_{DD}$ ) and on falling edge the load capacitance is discharged to GND.

Now suppose gate switches at some average frequency  $f_{sw}$  (switching frequency). Over the time period  $T$ , the load is charging and discharging. So average power dissipation is:

$$P_{dynamic} = C_L V_{DD}^2 f_{sw}$$

This is called dynamic power because it arises from the switching of the load.

The total power dissipation can be calculated as:

$$P_{total} = P_{static} + P_{dynamic}$$

## **PROCEDURE:**

### **For CMOS Inverter:**

1. Connect the circuit on breadboard according to the given Figure 1(a) for implementing CMOS inverter. Provide +5V to the circuit.

2. Note down the observed values in Table 1.

### **For Propagation Delay:**

1. Connect the circuit on breadboard according to the given Figure 3 for implementing CMOS inverter with the load capacitor of 0.1uF. Provide +5V  $V_{DD}$  to the circuit.

2. Apply 5V peak to peak square wave with 1 KHz frequency at the input of the CMOS inverter.

3. Observe the propagation delay directly on the oscilloscope by connecting both the input and output simultaneously.

4. Note down the values of  $tp_{HL}$ ,  $tp_{LH}$  and  $tp$  in Table 2.

5. Observe how increasing the output load capacitance (0.1uF and 1uF) affects the propagation delay.

### **For Power Dissipation:**

#### **Static Power:**

1. Connect the circuit on breadboard according to the given Figure 3 for implementing CMOS inverter. No need to connect a load capacitor. Provide +5V  $V_{DD}$  to the circuit.

2. Apply a stable input (0/1) to the input of the CMOS inverter.

3. Use a Digital Multimeter (DMM) in series with the power supply to measure the static current drawn from the supply.

4. Calculate the static power dissipation and note down the value in Table 3.

**Dynamic Power:**

1. Connect the circuit on breadboard according to the given Figure 3 for implementing CMOS inverter with a load capacitor of 1uF. Provide +5V  $V_{DD}$  to the circuit.

2. Apply 5V peak to peak square wave with 500 Hz frequency at the input of the CMOS inverter.

3. Calculate the dynamic power and total power dissipation of CMOS inverter and note down the values in Table 3.

4. Observe how the dynamic power increases with increase in input frequency (500 Hz and 1 KHz).

**OBSERVATIONS:****Table1: For CMOS Inverter**

| X (Input) | Y (Output) |

|-----------|------------|

| 0V        |            |

| 5V        |            |

**Table 2: For Propagation Delay of CMOS Inverter**

| Capacitor (0.1uF) |                 | Capacitor (1uF)   |                 |

|-------------------|-----------------|-------------------|-----------------|

| Propagation delay | Observed Values | Propagation delay | Observed Values |

| tp <sub>HL</sub>  |                 | tp <sub>HL</sub>  |                 |

| tp <sub>LH</sub>  |                 | tp <sub>LH</sub>  |                 |

| tp                |                 | tp                |                 |

**Table 3: For Power Dissipation of CMOS Inverter**

| Frequency (500 Hz) |                 | Frequency (1 KHz) |                 |

|--------------------|-----------------|-------------------|-----------------|

| Power Dissipation  | Observed Values | Power Dissipation | Observed Values |

| $P_{static}$       |                 | $P_{static}$      |                 |

| $P_{dynamic}$      |                 | $P_{dynamic}$     |                 |

| $P_{total}$        |                 | $P_{total}$       |                 |

## **CALCULATIONS:**

## **RESULTS:**

Total propagation delay of CMOS inverter for 0.1uF and 1uF is: \_\_\_\_\_

Total Power dissipation of CMOS inverter for 500 Hz and 1 KHz is: \_\_\_\_\_

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

Course Code and Title: EL-202 Integrated Circuits

| Psychomotor Domain Assessment Rubric-Level P3                                                                                              |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                 | Extent of Achievement                                                                            |                                                                                                       |                                                                                                       |                                                                                                         |                                                                                                    |

|                                                                                                                                            | 0                                                                                                | 1                                                                                                     | 2                                                                                                     | 3                                                                                                       | 4                                                                                                  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i> equipment and/or its component for a lab work.                         | Not able to identify the equipment.                                                              | --                                                                                                    | --                                                                                                    | --                                                                                                      | Able to identify equipment as well as its components.                                              |

| <b>Equipment Use</b><br>Sensory skills to <i>demonstrate</i> the use of the equipment for the lab work.                                    | Doesn't demonstrate the use of equipment.                                                        | Slightly demonstrates the use of equipment.                                                           | Somewhat demonstrates the use of equipment.                                                           | Moderately demonstrates the use of equipment.                                                           | Fully demonstrates the use of equipment.                                                           |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon sequence of steps in lab work.                                              | Not able to either learn or perform lab work procedure.                                          | Able to slightly understand lab work procedure and perform lab work.                                  | Able to somewhat understand lab work procedure and perform lab work.                                  | Able to moderately understand lab work procedure and perform lab work.                                  | Able to fully understand lab work procedure and perform lab work.                                  |

| <b>Response</b><br>Ability to <i>imitate</i> the lab work on his/her own.                                                                  | Not able to imitate the lab work.                                                                | Able to slightly imitate the lab work.                                                                | Able to somewhat imitate the lab work.                                                                | Able to moderately imitate the lab work.                                                                | Able to fully imitate the lab work.                                                                |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the observations from lab work for experimental verifications and illustrations. | Not able to use the observations from lab work for experimental verifications and illustrations. | Slightly able to use the observations from lab work for experimental verifications and illustrations. | Somewhat able to use the observations from lab work for experimental verifications and illustrations. | Moderately able to use the observations from lab work for experimental verifications and illustrations. | Fully able to use the observations from lab work for experimental verifications and illustrations. |

| <b>Safety Adherence</b><br>Adherence to <i>safety</i> procedures.                                                                          | Doesn't adhere to safety procedures.                                                             | Slightly adheres to safety procedures.                                                                | Somewhat adheres to safety procedures.                                                                | Moderately adheres to safety procedures.                                                                | Fully adheres to safety procedures.                                                                |

| <b>Equipment Handling</b><br><i>Equipment care</i> during the use.                                                                         | Doesn't handle equipment with required care.                                                     | Rarely handles equipment with required care.                                                          | Occasionally handles equipment with required care.                                                    | Often handles equipment with required care.                                                             | Handles equipment with required care.                                                              |

| <b>Group Work</b><br><i>Contributes</i> in a group based lab work.                                                                         | Doesn't participate and contribute.                                                              | Slightly participates and contributes.                                                                | Somewhat participates and contributes.                                                                | Moderately participates and contributes.                                                                | Fully participates and contributes.                                                                |

Laboratory Session No. \_\_\_\_\_

Date: \_\_\_\_\_

|                                   |  |

|-----------------------------------|--|

| Weighted CLO (Psychomotor Score)  |  |

| Remarks                           |  |

| Instructor's Signature with Date: |  |

# LAB SESSION 06

## **OBJECTIVE:**

To PRACTICE CMOS NAND gate and CMOS NOR gate and also TRY exclusive OR-gate (XOR) function.

## **EQUIPMENT REQUIRED:**

- Protoboard

- Function Generator

- Digital Multimeter

- Power Supply

- NMOS transistor 2N7000/IRF540 : 8

- PMOS transistor IRF9540 : 8

- LED

## **THEORY:**

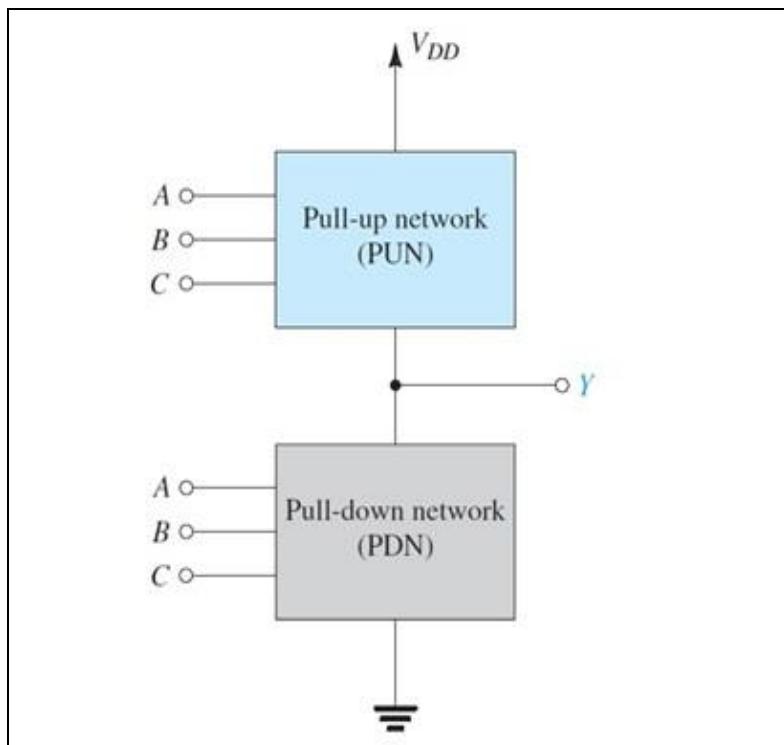

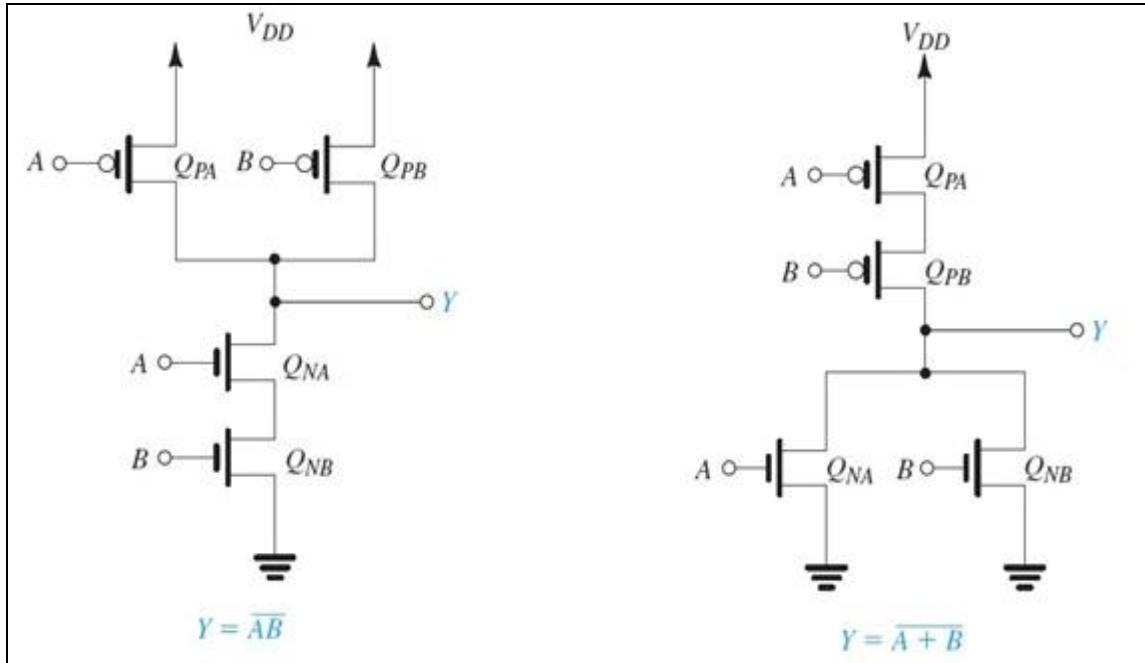

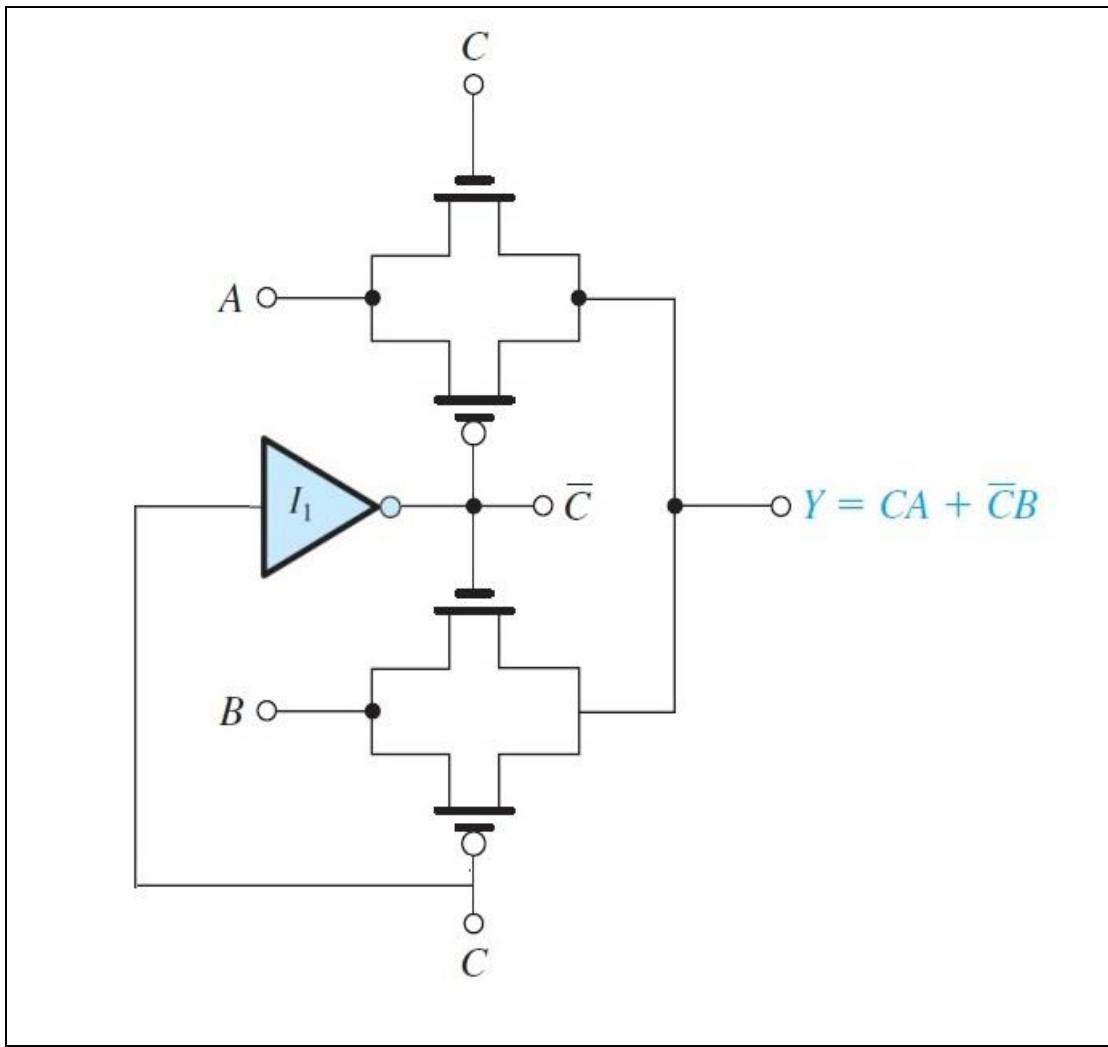

The CMOS logic gate consists of two networks: the pull-down network (PDN) constructed of NMOS transistors, and the pull-up network (PUN) constructed of PMOS transistors as shown in Figure 1. The two networks are operated by the input variables, in a complementary fashion.

**Figure 1: Representation of CMOS logic gate PUN comprises of PMOS transistor and PDN comprises of NMOS transistor**

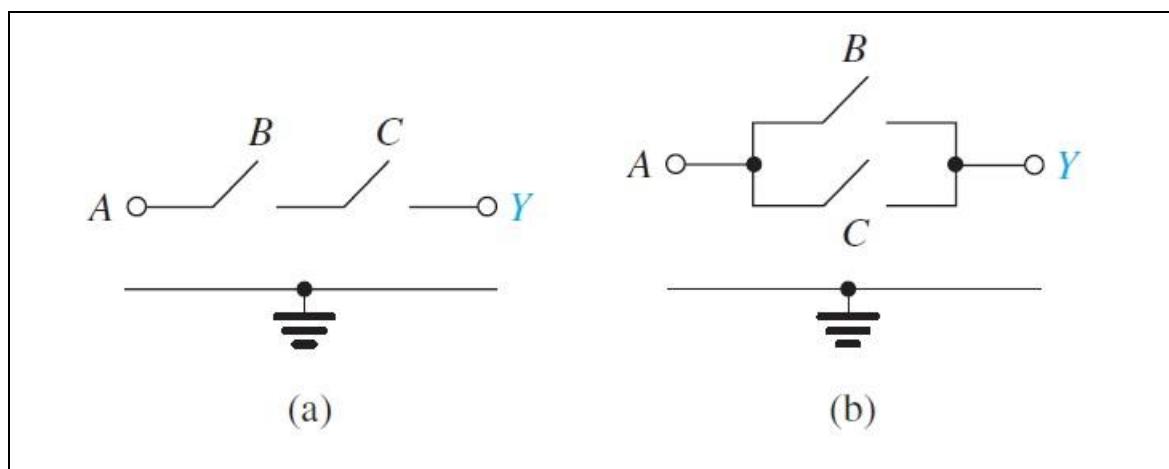

From the CMOS gate circuits, we observe that the PDN and the PUN are dual networks: Where a series branch exists in one, and a parallel branch exists in the other. Figure 2 shows a CMOS NAND gate and a CMOS NOR gate.

**Figure 2: (a) A two input CMOS NAND gate (b) A two input CMOS NOR gate**

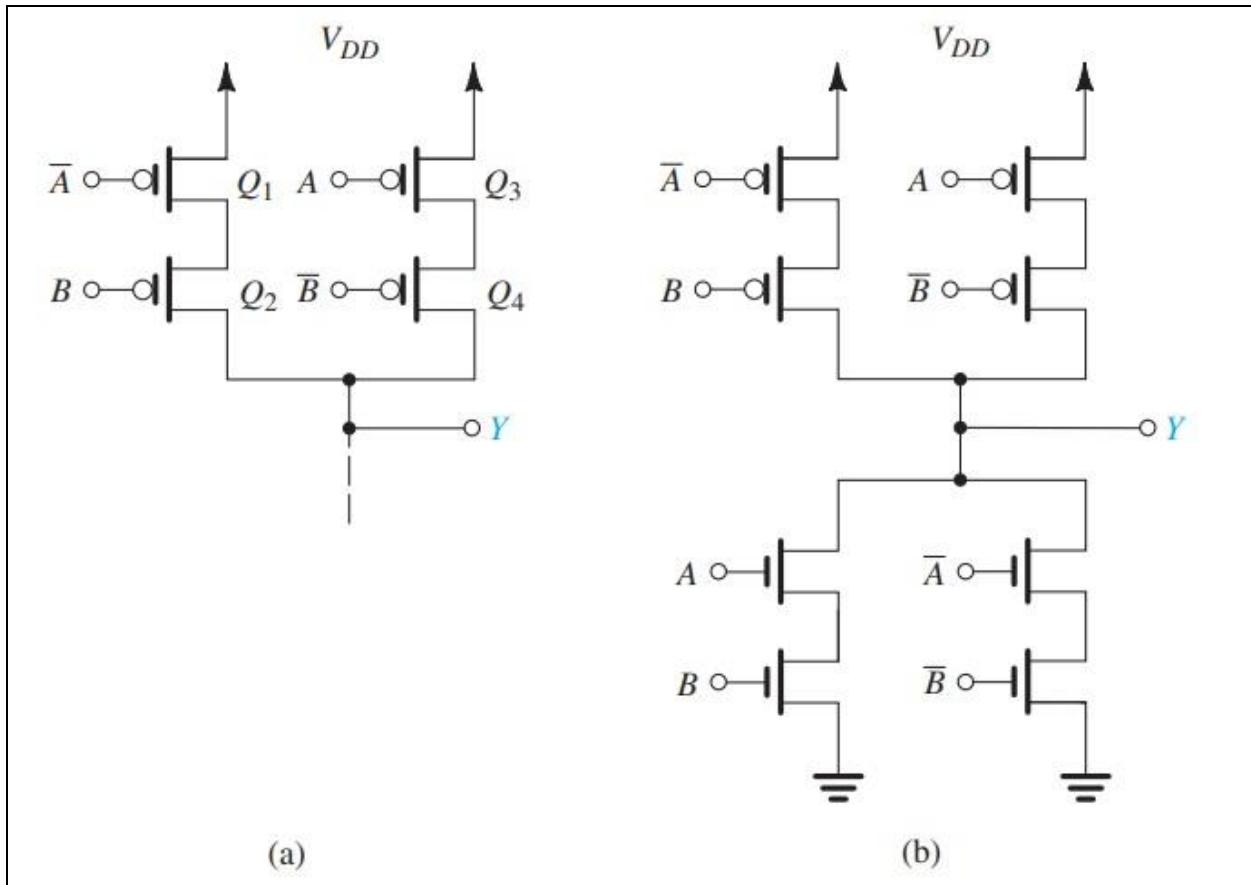

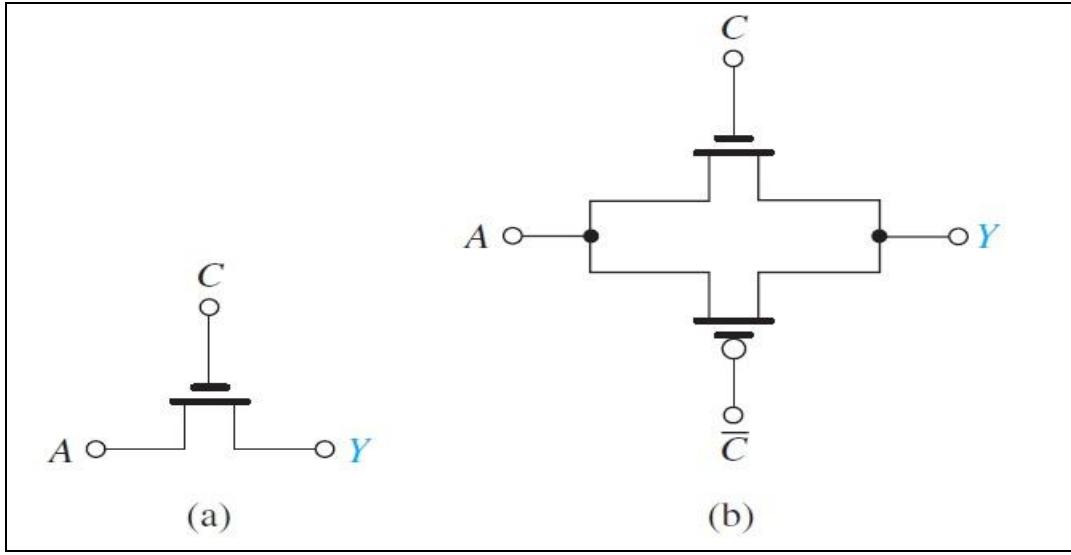

An important function that often arises in logic design is the exclusive-OR (XOR) function,

$$Y = A\bar{B} + \bar{A}B \quad (\text{Equation 1})$$

Here, Y (rather than  $\bar{Y}$ ) is given, it is easier to synthesize the PUN. However, that unfortunately Y is not a function of the complemented variables only (as we would like it to be). Thus, there will be a need of additional inverters. The PUN obtained directly from Equation 1 is shown in Figure 2(a). Note that the Q1, Q2 branch realizes the first term ( $A\bar{B}$ ), whereas the Q3, Q4 branch realizes the second term ( $\bar{A}B$ ). Note also the need for two additional inverters to generate  $\bar{A}$  and  $\bar{B}$ . As for synthesizing the PDN, it can be obtained as the dual network of the PUN in Figure 2(a). Alternatively, we can develop an expression for Y and use it to synthesize the PDN. Here, the direct synthesis approach is utilized. DeMorgan's law can be applied to the expression in Equation 1 to obtain  $\bar{Y}$  as:

$$\bar{Y} = AB + \bar{A}\bar{B} \quad (\text{Equation 2})$$

**Figure 3: Realization of exclusive-OR function (a) PUN synthesized directly from Equation 1 (b) Complete XOR realization utilizing PUN from equation 1 and PDN from Equation 2**

An interesting observation follows from the circuit in Figure 3(b). The PDN and the PUN here are not dual networks. Indeed, duality of the PDN and the PUN is not a necessary condition. Thus, although a dual of PDN (or PUN) can always be used for PUN (or PDN), the two networks are not necessarily duals.

### **PROCEDURE:**

1. Connect the circuit on breadboard according to the given Figure 2 for implementing CMOS logic gates. Provide +5V to the circuit.

2. For implementing NAND gate, connect the PDN with two NMOS transistors in series with A and B as the inputs and the PUN with two parallel PMOS transistors with A and B applied to their gates as inputs. Putting PDN and PUN together results in the CMOS NAND gate implementation as shown in Figure 2(a).

3. For implementing NOR gate, connect the PDN with two parallel NMOS devices with A and B as inputs and the PUN with two series PMOS devices with A and B as the inputs. Putting the PDN and the PUN together results in CMOS NOR gate implementation as shown in Figure 2(b).

4. Now note down the observed value of CMOS NAND and NOR gate in Table 1.

5. Connect the circuit on breadboard according to the given Figure 3(b) for implementing CMOS XOR function and note down the observed values in Table 2. Provide +5V to the circuit.

## **OBSERVATIONS:**

**Table 1: For CMOS NAND and NOR gate**

| CMOS NAND GATE |          |          | CMOS NOR GATE |          |          |

|----------------|----------|----------|---------------|----------|----------|

| <b>A</b>       | <b>B</b> | <b>Y</b> | <b>A</b>      | <b>B</b> | <b>Y</b> |

| 0V             | 0V       |          | 0V            | 0V       |          |

| 5V             | 0V       |          | 5V            | 0V       |          |

| 0V             | 5V       |          | 0V            | 5V       |          |

| 5V             | 5V       |          | 5V            | 5V       |          |

**Table 2: For CMOS exclusive-OR gate (XOR)**

| <b>A (Input)</b> | <b>B (Input)</b> | <b>Y (Output)</b> |

|------------------|------------------|-------------------|

| 0V               | 0V               |                   |

| 0V               | 5V               |                   |

| 5V               | 0V               |                   |

| 5V               | 5V               |                   |

F/OBEM 01/05/00

NED University of Engineering & Technology

Department of Electronic Engineering

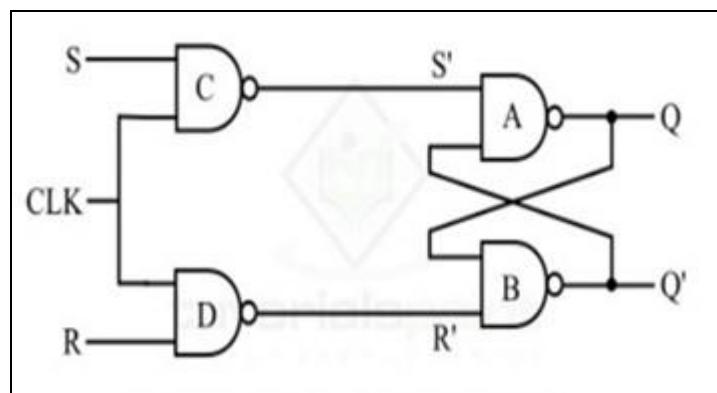

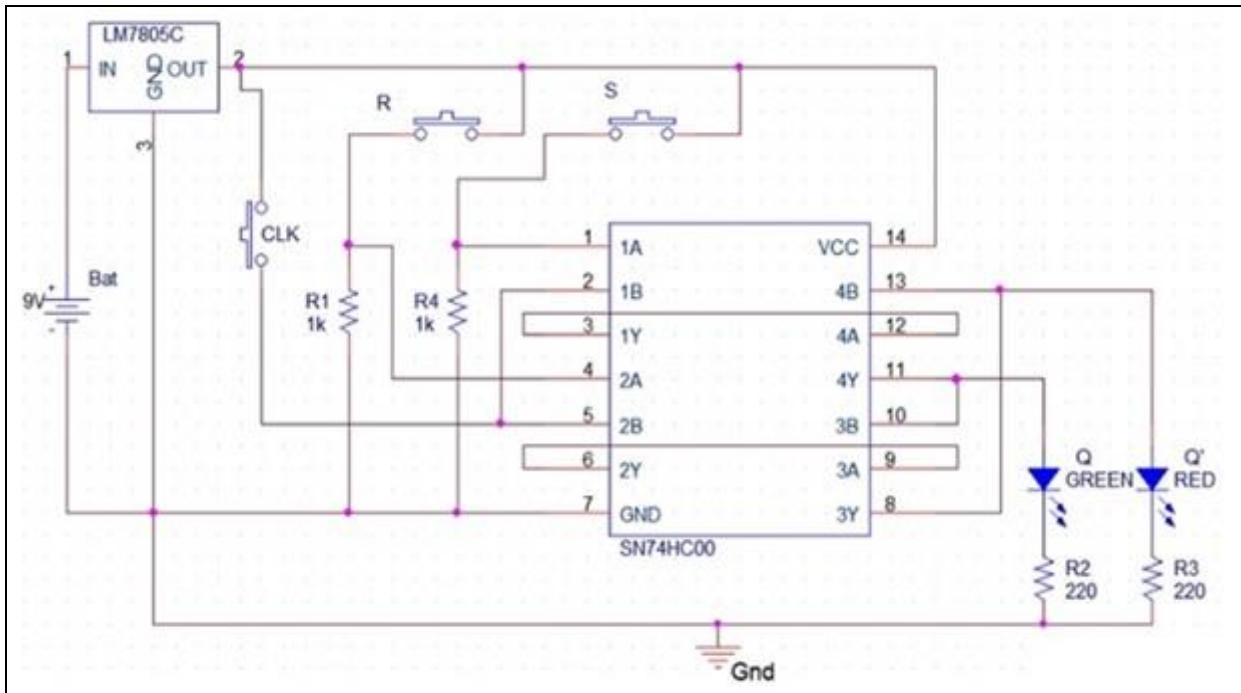

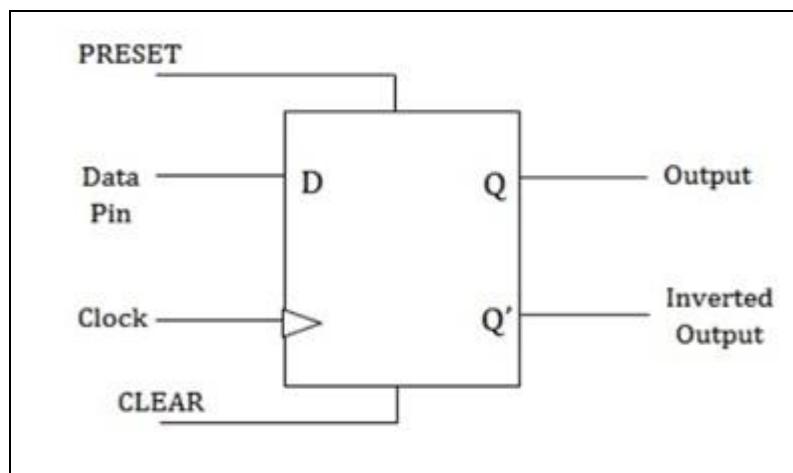

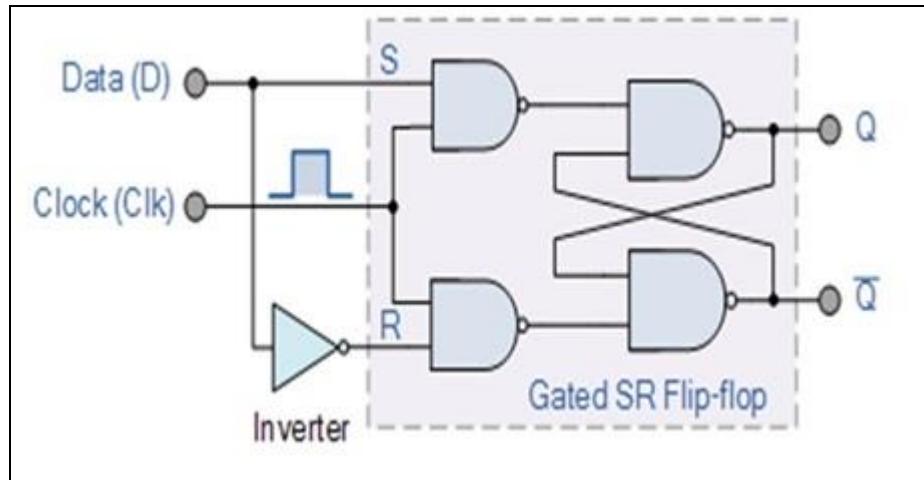

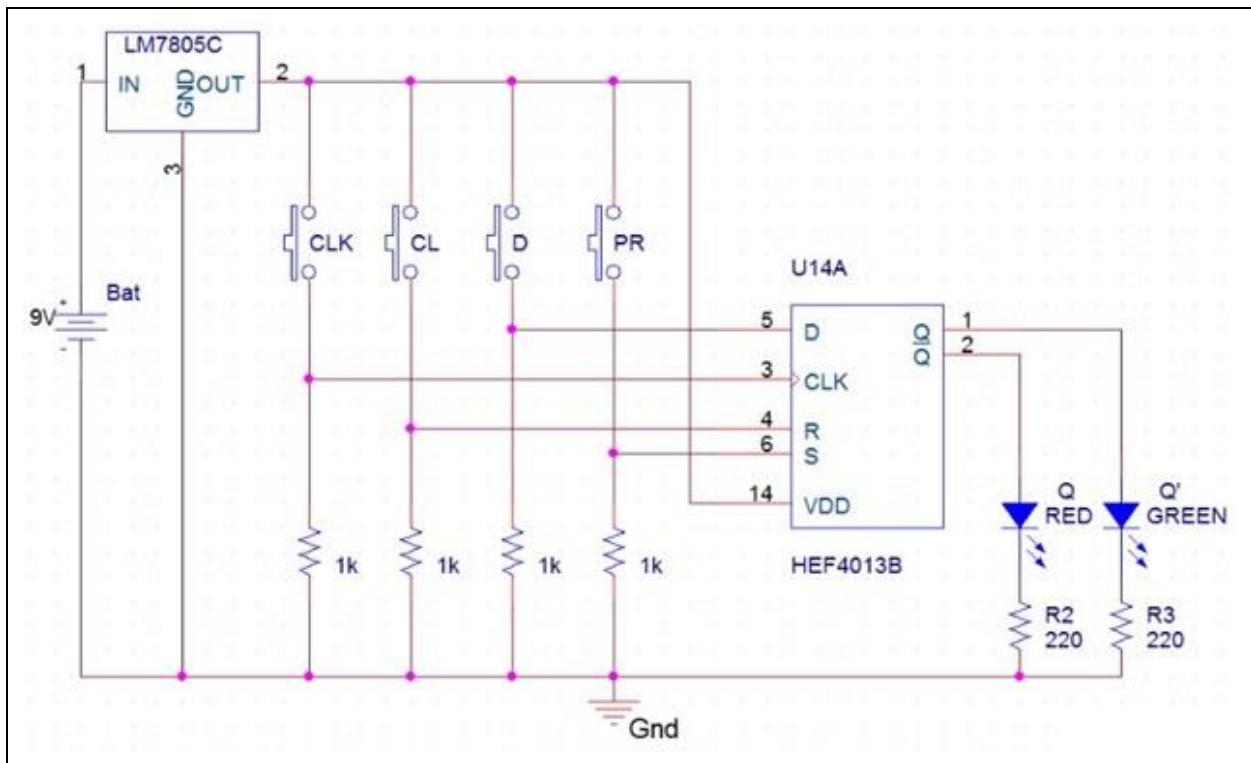

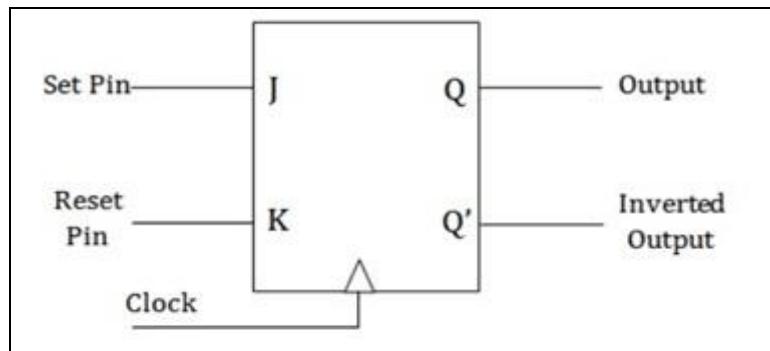

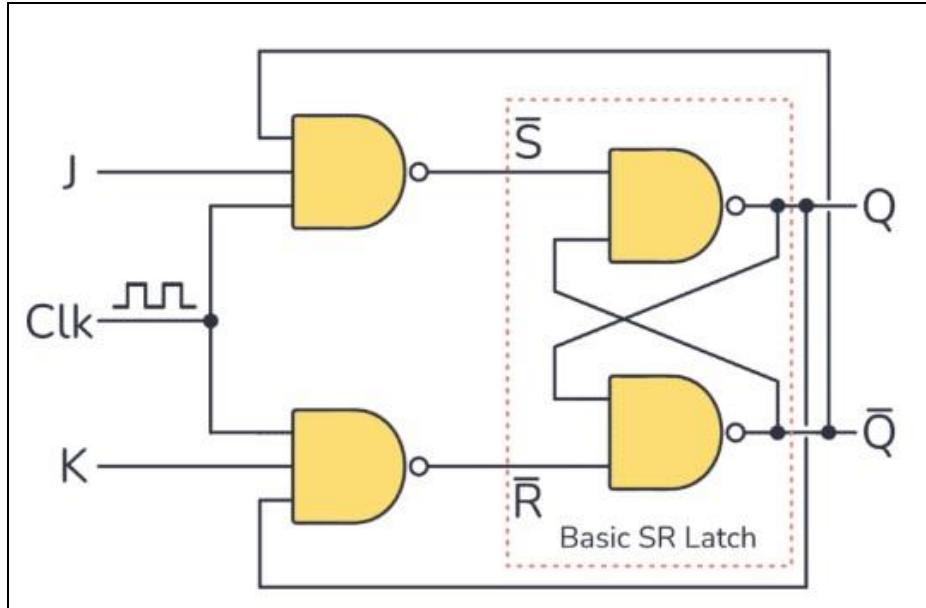

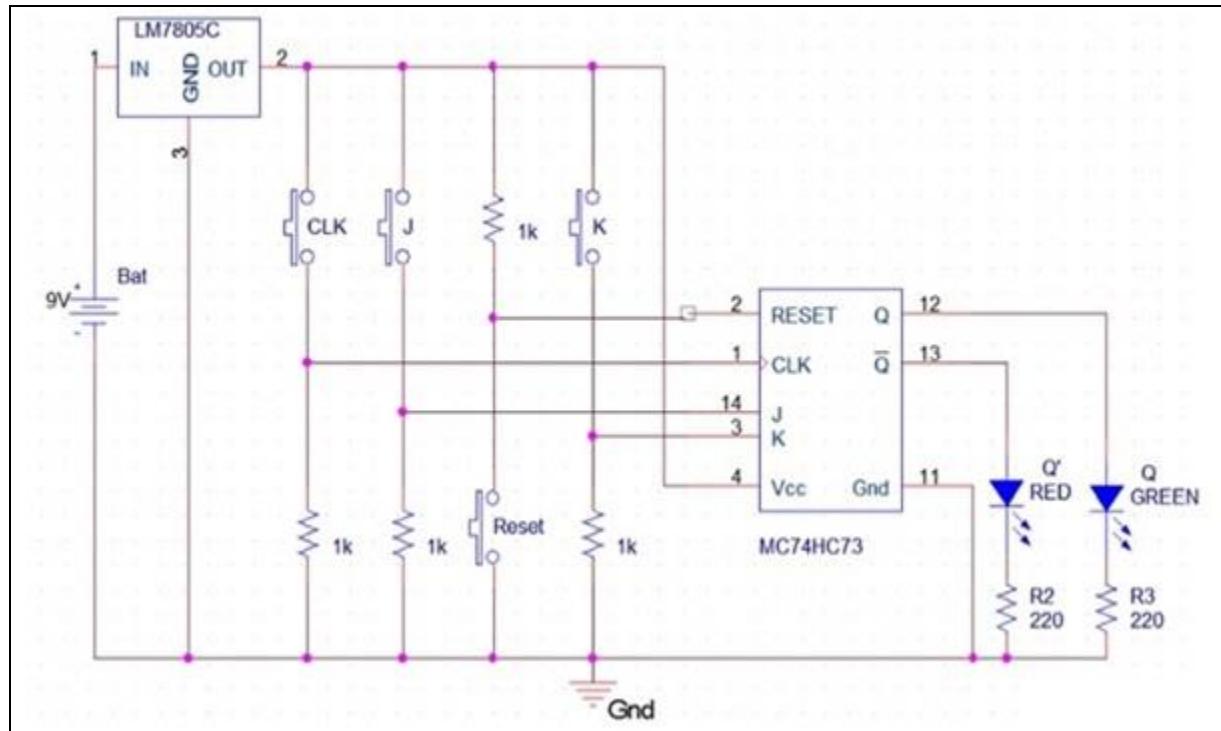

Course Code and Title: EL-202 Integrated Circuits