## **Department of Electronic Engineering NED University of Engineering & Technology**

## **PRACTICAL WORK BOOK**

For the course

# **VLSI SYSTEM DESIGN**

# (EL-408) For B.E(EL)

| Instructor's Name: |        |

|--------------------|--------|

| Student Name:      |        |

| Roll no:           | Batch: |

| Semester:          | Year:  |

| Department:        |        |

## LABORATORY WORK BOOK FOR THE COURSE

## VLSI System Design (EL-408)

Prepared By:

## Ms. Mariyum Jamshid (Lecturer)

Reviewed By:

## Ms. Madiha Mazhar (Lecturer)

Approved By: The Board of Studies of Department of Electronic Engineering

## VLSI System Design Laboratory CONTENTS

| S.  | Date | Page    | Psyc.      | CLO | List of Experiments                                                   | Marks  | Sign |

|-----|------|---------|------------|-----|-----------------------------------------------------------------------|--------|------|

| No. |      | No.     | Level      |     |                                                                       | Scored |      |

| 1   |      | 1       | P3         | 3   | To practice the following digital logic                               |        |      |

|     |      |         |            |     | circuits:                                                             |        |      |

|     |      |         |            |     | a) NMOS Inverter circuit with                                         |        |      |

|     |      |         |            |     | resistive load                                                        |        |      |

|     |      |         |            |     | b) NMOS AND, OR gates with                                            |        |      |

|     |      |         |            |     | resistive load                                                        |        |      |

|     |      |         |            |     | c) Implement a logic gate using<br>Pass transistors                   |        |      |

| 2   |      | 1       | P3         | 3   | To operate under supervision the                                      |        |      |

| 2   |      | 4       | r5         | 3   |                                                                       |        |      |

|     |      |         |            |     | operation of Digital-to-Analog and                                    |        |      |

| 3   |      | 10      | D2         | 3   | Analog to-Digital Convertor.                                          |        |      |

| 3   |      | 10      | P3         | 3   | To manipulate with guidance of Full Adder circuit.                    |        |      |

| 4   |      | 12      | P3         | 3   | To operate under supervision all types                                |        |      |

| 4   |      | 13      | F 5        | 3   | of Flip-Flops circuits.                                               |        |      |

| 5   |      | 25      | P3         | 3   | To imitate the 2-bit counter circuit                                  |        |      |

|     |      |         |            | 3   |                                                                       |        |      |

| 6   |      | 29      | P3         | 3   | To practice and verify the layout of a                                |        |      |

| 7   |      | 20      | P3         | 3   | CMOS inverter by using Microwind.<br>To operate under supervision the |        |      |

| /   |      | 32      | F 5        | 3   | layout of a CMOS NAND gate                                            |        |      |

|     |      |         |            |     | inverter by using Microwind.                                          |        |      |

| 8   |      | 34      | P3         | 3   | To imitate and verify the layout of                                   |        |      |

| U   |      | 54      | 15         | 5   | dynamic inverter logic by using                                       |        |      |

|     |      |         |            |     | Microwind.                                                            |        |      |

| 9   |      | 37      | P3         | 3   | To manipulate with guidance the                                       |        |      |

|     |      |         |            |     | layout of a logic function on CMOS                                    |        |      |

|     |      |         |            |     | logic by using Microwind.                                             |        |      |

| 10  |      | 40      | D2         | 3   | To practice all logic gates using                                     |        |      |

| 10  |      | 40      | P3         | 3   | Verilog HDL code on Modelsim                                          |        |      |

|     |      |         |            |     | Software.                                                             |        |      |

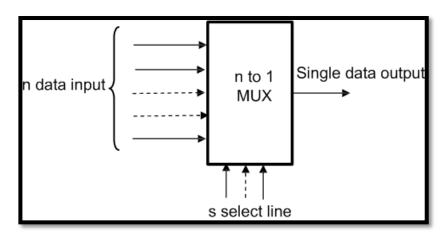

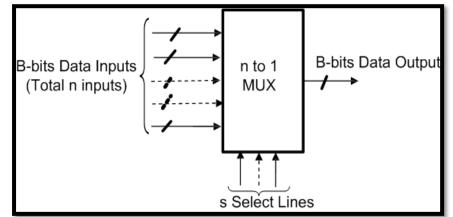

| 11  |      | 44      | P3         | 3   | To imitate the code of 4 to 1 MUX                                     |        |      |

|     |      |         |            |     | using Verilog HDL on Modelsim                                         |        |      |

|     |      |         |            |     | Software.                                                             |        |      |

|     |      |         |            |     |                                                                       |        |      |

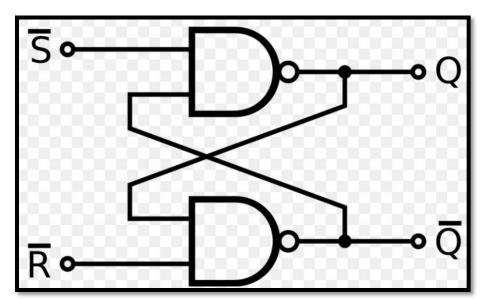

| 12  |      | 47      | P3         | 3   | To operate under supervision SR latch                                 |        |      |

|     |      |         |            |     | using Verilog HDL code on Quartus                                     |        |      |

|     |      |         |            |     | Software. Analyze the function of                                     |        |      |

|     |      |         |            |     | latch by testing code on ALTERA                                       |        |      |

| 10  |      | = = = = | <b>D</b> 2 | 2   | DE2 board                                                             |        |      |

| 13  |      | 52      | P3         | 3   | Open ended lab.                                                       |        |      |

|     |      |         |            |     |                                                                       |        |      |

## LAB SESSION NO 01

### **Objective:**

To practice the following digital logic circuits:

- a. NMOS Inverter circuit with resistive load

- b. NMOS AND, OR gates with resistive load

- c. Use pass transistors to implement 2 inputs AND

#### Apparatus:

- MOSFET transistors 2N7000

- Connecting Wires

- Digital Multimeter

- Proto-board

## **Theory:**

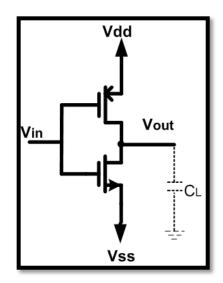

#### **Resistive Load Inverter**

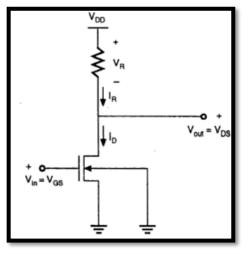

The basic structure of a resistive load inverter is shown in the figure given below. Here, enhancement type nMOS acts as the driver transistor. The load consists of a simple linear resistor  $R_L$ . The power supply of the circuit is  $V_{DD}$ .

#### **Circuit Operation**

When the input of the driver transistor is less than threshold voltage  $V_{TH}$  ( $V_{in} < V_{TH}$ ), driver transistor is in the cut – off region and does not conduct any current. So, the voltage drop across the load resistor is ZERO and output voltage is equal to the  $V_{DD}$ .

#### Figure 1.1: Structure of resistive load inverter

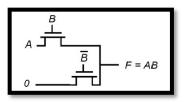

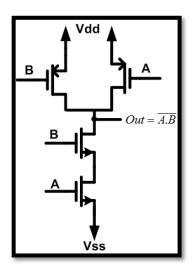

#### Pass Transistor

A transistor used as a switch to pass logic levels between nodes of a circuit, instead of as a switch connected directly to a supply voltage.

Figure 1.2: Design with Pass transistor logic

## **Procedure:**

#### <u>Part a</u>:

Connect the circuit on breadboard according to the given figure for implementing NMOS inverter.

#### **Observations:**

| Vin | Vout |

|-----|------|

| 0V  |      |

| 5V  |      |

#### Part b:

For implementing AND gate, connect two transistors in series and for OR gate, connect two transistors in parallel.

#### **Observations:**

| AND GATE |     |      | OR GATE |    |      |

|----------|-----|------|---------|----|------|

| V        | 'in | Vout | V       | in | Vout |

| 0V       | 0V  |      | 0V      | 0V |      |

| 5V       | 0V  |      | 5V      | 0V |      |

| 0V       | 5V  |      | 0V      | 5V |      |

| 5V       | 5V  |      | 5V      | 5V |      |

#### <u>Part c:</u>

Connect the circuit as shown in figure and implement AND operation.

### **Observations:**

#### NED University of Engineering & Technology Department of \_\_\_\_ELECTRONIC\_\_ Engineering Course Code and Title: \_\_\_\_EL-408 VLSI System Design\_

|                                                                                                                                          | Psychomoto                                                                                                      | r Domain Assessn                                                                                                        | nent Rubric-Level                                                                                                       | P3                                                                                                                        |                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                          |                                                                                                                 | H                                                                                                                       | Extent of Achievem                                                                                                      | ent                                                                                                                       |                                                                                                                   |

| Skill Sets                                                                                                                               | 0                                                                                                               | 1                                                                                                                       | 2                                                                                                                       | 3                                                                                                                         | 4                                                                                                                 |

| Equipment Identification<br>Sensory skill to <i>identify</i><br>equipment and/or its<br>component for a lab work.                        | Not able to identify the equipment.                                                                             |                                                                                                                         |                                                                                                                         |                                                                                                                           | Able to identify<br>equipment as well<br>as its components.                                                       |

| Equipment Use<br>Sensory skills to<br><i>demonstrate</i> the use of the<br>equipment for the lab<br>work.                                | Doesn't<br>demonstrate the<br>use of equipment.                                                                 | Slightly<br>demonstrates the<br>use of equipment.                                                                       | Somewhat<br>demonstrates the<br>use of equipment.                                                                       | Moderately demon<br>strates the use of<br>equipment.                                                                      | Fully<br>demonstrates the<br>use of equipment.                                                                    |

| <b>Procedural Skills</b><br><i>Displays</i> skills to act upon<br>sequence of steps in lab<br>work.                                      | Not able to either<br>learn or perform<br>lab work<br>procedure.                                                | Able to slightly<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to somewhat<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to moderately<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to fully<br>understand lab<br>work procedure<br>and perform lab<br>work.                                     |

| Response<br>Ability to <i>imitate</i> the lab<br>work on his/her own.                                                                    | Not able to<br>imitate the lab<br>work.                                                                         | Able to slightly imitate the lab work.                                                                                  | Able to somewhat<br>imitate the lab<br>work.                                                                            | Able to moderately imitate the lab work.                                                                                  | Able to fully<br>imitate the lab<br>work.                                                                         |

| Observation's Use<br>Displays skills to use the<br>observations from lab<br>work for experimental<br>verifications and<br>illustrations. | Not able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Slightly able to<br>use the<br>observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Somewhat able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Moderately able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Fully able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. |

| Safety Adherence<br>Adherence to <i>safety</i><br>procedures.                                                                            | Doesn't adhere to safety procedures.                                                                            | Slightly adheres<br>to safety<br>procedures.                                                                            | Somewhat<br>adheres to safety<br>procedures.                                                                            | Moderately adheres<br>to safety<br>procedures.                                                                            | Fully adheres to safety procedures.                                                                               |

| Equipment Handling<br>Equipment care during the<br>use.                                                                                  | Doesn't handle<br>equipment with<br>required care.                                                              | Rarely handles<br>equipment with<br>required care.                                                                      | Occasionally<br>handles<br>equipment with<br>required care.                                                             | Often handles<br>equipment with<br>required care.                                                                         | Handles<br>equipment with<br>required care.                                                                       |

| Group Work<br>Contributes in a group<br>based lab work.                                                                                  | Doesn't<br>participate and<br>contribute.                                                                       | Slightly<br>participates and<br>contributes.                                                                            | Somewhat<br>participates and<br>contributes.                                                                            | Moderately<br>participates and<br>contributes.                                                                            | Fully participates and contributes.                                                                               |

| Laboratory Session                                                                                                                       |                                                                                                                 |                                                                                                                         | Dat                                                                                                                     | te:                                                                                                                       |                                                                                                                   |

| Weighted CLO (Ps                                                                                                                         | ychomotor Score)                                                                                                |                                                                                                                         |                                                                                                                         |                                                                                                                           |                                                                                                                   |

Weighted CLO (Psychomotor Score)

Remarks

Instructor's Signature with Date:

## LAB SESSION NO 02

### **Objective:**

To operate under supervision the operation of Digital-to-Analog and Analog-to-Digital Convertor.

#### <u>Apparatus:</u>

- 2-bit priority encoder IC

- Resistor sheet

- LEDS

- Connecting Wires

- Digital Multimeter

- Bread Board

- 7408 IC (AND)

- 7432 IC (OR)

- 7486 IC (XOR)

- 4049 IC (INVERTER)

- LF351 OPAMP

- Switches

- Protoboard

## **Theory:**

#### ANALOG TO DIGITAL CONVERTER:

An analog-to-digital (A/D) conversion means quantizing the amplitude of a physical quantity (e.g., a voltage) into a discrete levels class. Thus, obtaining a series of digits, forming a number of a proper code. Generally, the binary code and, consequently, binary numbers are used. Analog data can be obtained again through digital-to-analog (D/A) conversion.

Due to the quantization, each value V of the analog signal included within the interval  $V_i$  to  $V_{i+1}$  is always quantized at the same level  $N_i$ .

The interval:  $V_{i+1}$  to  $V_1 = Q$ , is defined as "quantum level".

Another important parameter of A/D converters is the conversion time since it defines the capacity of the converter to operate the conversion of a variable signal; in fact, remember that the sequence of the quantized levels must allow the regeneration of the original analog signal.

A time-variable signal can be converted into a discrete values class carrying out the sampling and holding operations. The sampling and holding operations are carried out through proper circuits called "Sample and Hold".

#### Resolution

It defines the smallest standard incremental change in. the output voltage of a DAC or the amount of input voltage change required to increment the output of an ADC between a code change and

the next adjacent code change. A converter with "n" switches can divide the input in  $2^n$  parts: the

least significant increment is then  $2^{-n}$ , or one least significant bit (LSB). On the contrary the Most Significant Bit carries a weight of 2. Resolution is applied to DACs and ADCs and may be expressed in percent of full scale or in binary bits.

#### **Circuit Operation:**

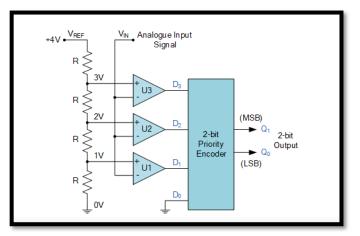

#### 2-bit Analogue to Digital Converter Circuit

In general,  $2^{n}$ -1 comparators would be required for conversion of an "n"-bit binary output, where "n" is typically in the range from 8 to 16. If we create a 2-bit ADC, then we will need  $2^{2}$ -1 which is "3" comparators as we need four different voltage levels corresponding to the 4 digital values required for a 4-to-2-bit encoder circuit as shown.

Figure 2.1: 2-bit analogue to digital converter circuit

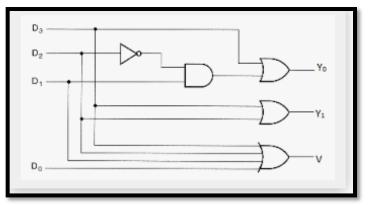

Encoder alternate circuit:

Figure 2.2: Encoder circuit

Step size= analog voltage/ no of bits

#### **DIGITAL TO ANALOG CONVERTER:**

It is often necessary to convert analog signal to an accurate digital number, and vice versa. For example, in applications where a microprocessor is controlling an experiment, the analog signal from a sensor needs to be converted into digital form so it can be communicated to the microprocessor. After the processing takes place in the digital form, the output from the microcontroller needs to be converted back to the analog form to communicate with the analog world. In this lab session we will consider the case of digital to analog conversion (DAC). A digital to analog converter (DAC) converts a digital signal to an analog voltage or current output. Many types of DACs are available and usually switches, resistors, and op-amps are used to implement the conversion.

#### **Circuit Operation:**

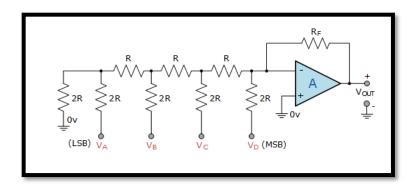

#### **R-2R Ladder Digital to Analog Converter (DAC)**

R-2R Ladder is another type of DAC based on the opamp summing amplifier It uses only two values of resistors which makes the fabrication of the circuit easier and more accurate. R-2R ladder can scalable to any number of bits desired and its output impedance will remain R, regardless the number of bits. Each bit corresponds to a switch.

Figure 2.3: R-2R ladder digital to analogue converter circuit

If the bit is high, the corresponding switch is connected to the inverting input of the op-amp. If the bit is low, the corresponding switch is connected to ground.

bn means Bit n, hence;

If bit n is set, bn=1

If bit n is clear, bn=0

For a 4-Bit R-2R Ladder, output is equal to;

$$V_{out} = -V_{ref} \left( b_3 + b_2 \frac{1}{2} + b_1 \frac{1}{4} + b_0 \frac{1}{8} \right)$$

In order to understand this, let's solve an example:

If we have the Vref = 2.4 V, and we need to convert the digital number 7 (which is 0111 in binary form) into analog then by applying the following equation, we get:

$V_{out} = -V_{ref} (b_3 + b_2 \frac{1}{2} + b_1 \frac{1}{4} + b_0 \frac{1}{8})$   $V_{out} = -2.4 [(0) + (1*1/2) + (1*1/4) + (1*1/8)]$   $V_{out} = -2.4 [0 + 1/2 + 1/4 + 1/8]$   $V_{out} = -2.4 * 7/8$  $V_{out} = -2.1 V$

So, from the above example, we get that the voltage measured by the multimeter will be -2.1 V

#### **Procedure:**

#### a) FOR ADC

Connect the circuit on breadboard according to the given figure for implementing ADC converter

#### **Observation:**

The resulting truth table by implementing ADC converter circuit is as follows

| ANALOG INPUT  | C  | OMPARAT       | DIGITAL | OUTPUTS |    |    |

|---------------|----|---------------|---------|---------|----|----|

| VOLATGE (VIN) | D3 | D3 D2 D1 D0 0 |         |         | Q1 | Q0 |

|               |    |               |         |         |    |    |

|               |    |               |         |         |    |    |

|               |    |               |         |         |    |    |

|               |    |               |         |         |    |    |

#### b) FOR DAC

Connect the circuit on breadboard according to the given figure for implementing DAC converter.

#### **Observation:**

The resulting truth table by implementing DAC converter circuit is as follows

| DECIMAL NUMERALS |    | DIGITA | LINPUT |    | ANALOG OUTPUT |

|------------------|----|--------|--------|----|---------------|

| DECIMAL          | D3 | D2     | D1     | D0 | VOUT          |

| 0                |    |        |        |    |               |

| 1                |    |        |        |    |               |

| 2                |    |        |        |    |               |

| 3                |    |        |        |    |               |

| 4                |    |        |        |    |               |

| 5                |    |        |        |    |               |

| 6                |    |        |        |    |               |

| 7                |    |        |        |    |               |

| 8                |    |        |        |    |               |

| 9                |    |        |        |    |               |

| 10               |    |        |        |    |               |

| 11               |    |        |        |    |               |

| 12               |    |        |        |    |               |

| 13               |    |        |        |    |               |

| 14               |    |        |        |    |               |

| 15               |    |        |        |    |               |

#### NED University of Engineering & Technology Department of \_\_\_\_ELECTRONIC\_\_ Engineering Course Code and Title: \_\_\_\_EL-408 VLSI System Design\_

|                                                                                                                                                        | Psychomotol                                                                                                     | r Domain Assessn                                                                                                        | nent Rubric-Level                                                                                                       | P3                                                                                                                        |                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Skill Sets                                                                                                                                             |                                                                                                                 | H                                                                                                                       | Extent of Achievem                                                                                                      | ent                                                                                                                       | 1                                                                                                                 |

| Skill Sels                                                                                                                                             | 0                                                                                                               | 1                                                                                                                       | 2                                                                                                                       | 3                                                                                                                         | 4                                                                                                                 |

| Equipment Identification<br>Sensory skill to <i>identify</i><br>equipment and/or its<br>component for a lab work.                                      | Not able to identify the equipment.                                                                             |                                                                                                                         | -                                                                                                                       |                                                                                                                           | Able to identify<br>equipment as well<br>as its components                                                        |

| Equipment Use<br>Sensory skills to<br><i>demonstrate</i> the use of the<br>equipment for the lab<br>work.                                              | Doesn't<br>demonstrate the<br>use of equipment.                                                                 | Slightly<br>demonstrates the<br>use of equipment.                                                                       | Somewhat<br>demonstrates the<br>use of equipment.                                                                       | Moderately demon<br>strates the use of<br>equipment.                                                                      | Fully<br>demonstrates the<br>use of equipment.                                                                    |

| <b>Procedural Skills</b><br><b>Displays</b> skills to act upon<br>sequence of steps in lab<br>work.                                                    | Not able to either<br>learn or perform<br>lab work<br>procedure.                                                | Able to slightly<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to somewhat<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to moderately<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to fully<br>understand lab<br>work procedure<br>and perform lab<br>work.                                     |

| Response<br>Ability to <i>imitate</i> the lab<br>work on his/her own.                                                                                  | Not able to<br>imitate the lab<br>work.                                                                         | Able to slightly imitate the lab work.                                                                                  | Able to somewhat<br>imitate the lab<br>work.                                                                            | Able to moderately<br>imitate the lab<br>work.                                                                            | Able to fully<br>imitate the lab<br>work.                                                                         |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the<br>observations from lab<br>work for experimental<br>verifications and<br>illustrations. | Not able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Slightly able to<br>use the<br>observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Somewhat able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Moderately able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Fully able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. |

| Safety Adherence<br>Adherence to safety<br>procedures.                                                                                                 | Doesn't adhere to safety procedures.                                                                            | Slightly adheres<br>to safety<br>procedures.                                                                            | Somewhat<br>adheres to safety<br>procedures.                                                                            | Moderately adheres<br>to safety<br>procedures.                                                                            | Fully adheres to safety procedures.                                                                               |

| Equipment Handling<br>Equipment care during the<br>use.                                                                                                | Doesn't handle<br>equipment with<br>required care.                                                              | Rarely handles<br>equipment with<br>required care.                                                                      | Occasionally<br>handles<br>equipment with<br>required care.                                                             | Often handles<br>equipment with<br>required care.                                                                         | Handles<br>equipment with<br>required care.                                                                       |

| Group Work<br>Contributes in a group<br>based lab work.                                                                                                | Doesn't<br>participate and<br>contribute.                                                                       | Slightly<br>participates and<br>contributes.                                                                            | Somewhat<br>participates and<br>contributes.                                                                            | Moderately<br>participates and<br>contributes.                                                                            | Fully participates and contributes.                                                                               |

| Laboratory Session                                                                                                                                     | No02                                                                                                            |                                                                                                                         | Dat                                                                                                                     | e:                                                                                                                        |                                                                                                                   |

| Weighted CLO (Psychomotor Score)  |  |

|-----------------------------------|--|

| Remarks                           |  |

| Instructor's Signature with Date: |  |

## LAB SESSION NO 03

## <u>Objective:</u>

To manipulate with guidance of Full Adder circuit.

### Apparatus:

- Digital multimeter

- Bread Board

- 7408 IC (AND)

- 7432 IC (OR)

- 7486 IC (XOR)

- LEDS

- Resistor sheet

- Connecting wires

- Supply or Battery

## **Theory:**

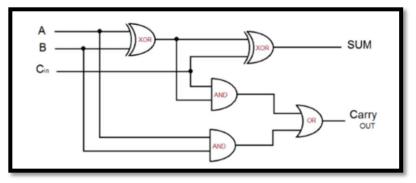

#### <u>Full- Adder</u>

A full-adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs. Two of the input variables, denoted by x and y, represent two significant bits to be added. The third input z, represents the carry from the previous lower significant position. Two outputs are necessary because the arithmetic sum of three binary digits ranges in value from 0 to3 and binary 2or 3 needs two digits. The binary variable S indicates the sum and C the carry. The binary variable S gives the value if the least significant bit of the sum. The binary variable C gives the output carry.

### **Procedure:**

- Implement the circuit of full adder on bread board

- Supply the required power (5V) to ICs AND OR and XOR

- Check the output using logic probe or LEDs and fill in the truth table

Figure 3.1: Full adder circuit

## **Observation:**

The resulting truth table of the adder circuit is as follows:

| А | В | CIN | COUT | S |

|---|---|-----|------|---|

| 0 | 0 | 0   |      |   |

| 0 | 0 | 1   |      |   |

| 0 | 1 | 0   |      |   |

| 0 | 1 | 1   |      |   |

| 1 | 0 | 0   |      |   |

| 1 | 0 | 1   |      |   |

| 1 | 1 | 0   |      |   |

| 1 | 1 | 1   |      |   |

#### NED University of Engineering & Technology Department of \_\_\_\_ELECTRONIC\_\_ Engineering Course Code and Title: \_\_\_\_EL-408 VLSI System Design\_

| Sensory skill to <i>identify</i><br>equipment and/or its<br>component for a lab work.<br>Equipment Use<br>Sensory skills to<br><i>demonstrate</i> the use of the<br>equipment for the lab<br>work.<br>Procedural Skills<br>Displays skills to act upon | Psychomotor Domain Assessment Rubric-Level P3                                                                   |                                                                                                                         |                                                                                                                         |                                                                                                                           |                                                                                                                   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Equipment IdentificationSensory skill to identifyequipment and/or itscomponent for a lab work.Equipment UseSensory skills todemonstratethe use of theequipment for the labwork.Procedural SkillsDisplays skills to act upon                            |                                                                                                                 | F                                                                                                                       | Extent of Achievem                                                                                                      | ent                                                                                                                       |                                                                                                                   |  |  |

| Sensory skill to <i>identify</i><br>equipment and/or its<br>component for a lab work.<br>Equipment Use<br>Sensory skills to<br><i>demonstrate</i> the use of the<br>equipment for the lab<br>work.<br>Procedural Skills<br>Displays skills to act upon | 0                                                                                                               | 1                                                                                                                       | 2                                                                                                                       | 3                                                                                                                         | 4                                                                                                                 |  |  |

| Sensory skills to demonstrate the use of the equipment for the lab work. Procedural Skills Displays skills to act upon                                                                                                                                 | Not able to identify the equipment.                                                                             |                                                                                                                         |                                                                                                                         |                                                                                                                           | Able to identify<br>equipment as well<br>as its components.                                                       |  |  |

| Displays skills to act upon                                                                                                                                                                                                                            | Doesn't<br>demonstrate the<br>use of equipment.                                                                 | Slightly<br>demonstrates the<br>use of equipment.                                                                       | Somewhat<br>demonstrates the<br>use of equipment.                                                                       | Moderately demon<br>strates the use of<br>equipment.                                                                      | Fully<br>demonstrates the<br>use of equipment.                                                                    |  |  |

| work.                                                                                                                                                                                                                                                  | Not able to either<br>learn or perform<br>lab work<br>procedure.                                                | Able to slightly<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to somewhat<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to moderately<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to fully<br>understand lab<br>work procedure<br>and perform lab<br>work.                                     |  |  |

| Ability to <i>imitate</i> the lab                                                                                                                                                                                                                      | Not able to<br>imitate the lab<br>work.                                                                         | Able to slightly imitate the lab work.                                                                                  | Able to somewhat<br>imitate the lab<br>work.                                                                            | Able to moderately imitate the lab work.                                                                                  | Able to fully<br>imitate the lab<br>work.                                                                         |  |  |

| Displays skills to use the<br>observations from lab<br>work for experimental<br>verifications and                                                                                                                                                      | Not able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Slightly able to<br>use the<br>observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Somewhat able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Moderately able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Fully able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. |  |  |

|                                                                                                                                                                                                                                                        | Doesn't adhere to safety procedures.                                                                            | Slightly adheres<br>to safety<br>procedures.                                                                            | Somewhat<br>adheres to safety<br>procedures.                                                                            | Moderately adheres<br>to safety<br>procedures.                                                                            | Fully adheres to safety procedures.                                                                               |  |  |

| Equipment care during the                                                                                                                                                                                                                              | Doesn't handle<br>equipment with<br>required care.                                                              | Rarely handles<br>equipment with<br>required care.                                                                      | Occasionally<br>handles<br>equipment with<br>required care.                                                             | Often handles<br>equipment with<br>required care.                                                                         | Handles<br>equipment with<br>required care.                                                                       |  |  |

| <i>Contributes</i> in a group based lab work.                                                                                                                                                                                                          | Doesn't<br>participate and<br>contribute.                                                                       | Slightly<br>participates and<br>contributes.                                                                            | Somewhat<br>participates and<br>contributes.                                                                            | Moderately<br>participates and<br>contributes.                                                                            | Fully participates and contributes.                                                                               |  |  |

| Laboratory Session N                                                                                                                                                                                                                                   | No03                                                                                                            |                                                                                                                         | Dat                                                                                                                     | e:                                                                                                                        |                                                                                                                   |  |  |

| Weighted CLO (Psyc                                                                                                                                                                                                                                     |                                                                                                                 |                                                                                                                         |                                                                                                                         |                                                                                                                           |                                                                                                                   |  |  |

Instructor's Signature with Date:

Remarks

## LAB SESSION NO 04

### **Objective:**

To operate under supervision all types of Flip-Flops circuits.

#### Apparatus:

- MC74HC73A (Dual JK flip-flop)

- HEF4013B (Dual D flip-flop)

- LM7805

- Switches

- Supply

- LEDS

- Resistor sheet

- Breadboard

- Connecting wires

- 7408 IC (AND)

- 7432 IC (OR)

- 7486 IC (XOR)

- 4049 IC (INVERTER)

- 7400 IC (NAND)

## **Theory:**

The bistable multivibrator, commonly called flip- flops, are the most common form of digital memory elements. A memory element is generally a device which can store the logic state 0 or 1, called information "bit". The memory elements enable the storing of digital information for further uses. They permit to carry out complex sequential digital circuits, which took to the construction of modern calculators.

#### **Types of Flip Flop**

There are basically 4 types of flip-flops:

- 1. SR Flip Flop

- 2. JK Flip Flop

- 3. D Flip Flop

- 4. T Flip Flop

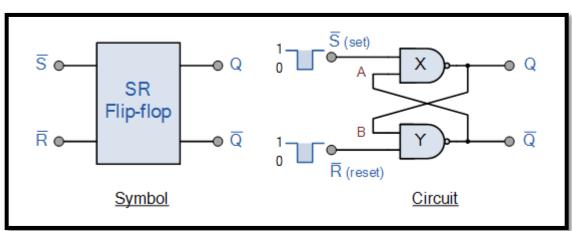

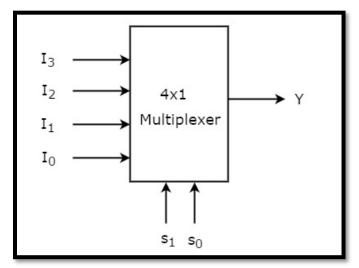

#### 1)<u>S-R Flip-flop (latch):</u>

The **SR flip-flop**, also known as a *SR Latch*, can be considered as one of the most basic sequential logic circuit possible. This simple flip-flop is basically a one-bit memory bistable device that has two inputs, one which will "SET" the device (meaning the output = "1"), and is labelled **S** and one which will "RESET" the device (meaning the output = "0"), labelled **R**.

Then the SR description stands for "Set-Reset". The reset input resets the flip-flop back to its original state with an output Q that will be either at a logic level "1" or logic "0" depending upon this set/reset condition.

A basic NAND gate SR flip-flop circuit provides feedback from both of its outputs back to its opposing inputs and is commonly used in memory circuits to store a single data bit. Then the SR flip-flop actually has three inputs, Set, Reset and its current output Q relating to its current state or history.

The term "Flip-flop" relates to the actual operation of the device, as it can be "flipped" into one logic Set state or "flopped" back into the opposing logic Reset state.

The simplest way to make any basic single bit set-reset SR flip-flop is to connect together a pair of cross-coupled 2-input NAND gates as shown, to form a Set-Reset Bistable also known as an active LOW SR NAND Gate Latch, so that there is feedback from each output to one of the other NAND gate inputs.

This device consists of two inputs, one called the *Set*, S and the other called the *Reset*, R with two corresponding outputs Q and its inverse or complement Q (not-Q)

#### **Basic RS Flip Flop circuit and symbol:**

Figure 4.1: S-R Flip-flop symbol and circuit

#### The Set State

Consider the circuit shown above. If the input R is at logic level "0" (R = 0) and input S is at logic level "1" (S = 1), the NAND gate Y has at least one of its inputs at logic "0" therefore, its output Q must be at a logic level "1" (NAND Gate principles). Output Q is also fed back to input "A" and so both inputs to NAND gate X are at logic level "1", and therefore its output Q must be at logic level "0".

Again, NAND gate principals. If the reset input R changes state, and goes HIGH to logic "1" with S remaining HIGH also at logic level "1", NAND gate Y inputs are now R = "1" and B = "0". Since one of its inputs is still at logic level "0" the output at Q still remains HIGH at logic level "1" and there is no change of state. Therefore, the flip-flop circuit is said to be "Latched" or "Set" with Q = "1" and Q = "0".

#### The Reset State

In this second stable state, Q is at logic level "0", (not Q = "0") its inverse output at Q is at logic level "1", (Q = "1"), and is given by R = "1" and S = "0".

As gate *X* has one of its inputs at logic "0" its output Q must equal logic level "1" (again NAND gate principles). Output Q is fed back to input "B", so both inputs to NAND gate *Y* are at logic "1", therefore, Q = "0".

If the set input, S now changes state to logic "1" with input R remaining at logic "1", output Q still remains LOW at logic level "0" and there is no change of state. Therefore, the flip-flop circuits "Reset" state has also been latched and we can define this "set/reset" action in the following truth table.

| State   | S | R | Q | ą | Description              |

|---------|---|---|---|---|--------------------------|

| Set     | 1 | 0 | 0 | 1 | Set Q » 1                |

| 561     | 1 | 1 | 0 | 1 | no change                |

| Reset   | 0 | 1 | 1 | 0 | Reset $\overline{Q} > 0$ |

| Reset   | 1 | 1 | 1 | 0 | no change                |

| Invalid | 0 | 0 | 1 | 1 | Invalid Condition        |

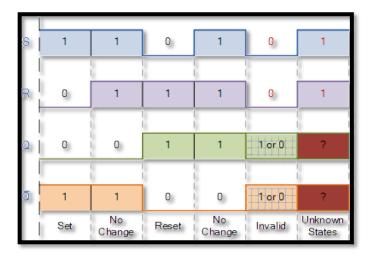

Figure 4.2: The Truth Table for the S-R Function

It can be seen that when both inputs S = "1" and R = "1" the outputs Q and Q can be at either logic level "1" or "0", depending upon the state of the inputs S or R BEFORE this input condition existed. Therefore, the condition of S = R = "1" does not change the state of the outputs Q and Q.

However, the input state of S = "0" and R = "0" is an undesirable or invalid condition and must be avoided. The condition of S = R = "0" causes both outputs Q and Q to be HIGH together at logic level "1" when we would normally want Q to be the inverse of Q.

The result is that the flip-flop loses control of Q and Q, and if the two inputs are now switched "HIGH" again after this condition to logic "1", the flip-flop becomes unstable and switches to an unknown data state based upon the unbalance as shown in the following switching diagram.

Figure 4.3: S-R Flip-flop Switching Diagram:

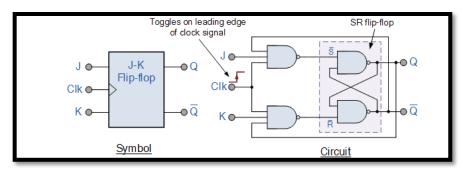

#### 2)<u>J-K flip-flop</u>

The sequential operation of the JK flip flop is exactly the same as for the previous SR flip-flop with the same "Set" and "Reset" inputs. The difference this time is that the "JK flip flop" has no invalid or forbidden input states of the SR Latch even when S and R are both at logic "1".

The **JK flip flop** is basically a gated SR flip-flop with the addition of a clock input circuitry that prevents the illegal or invalid output condition that can occur when both inputs S and R are equal to logic level "1". Due to this additional clocked input, a JK flip-flop has four possible input combinations, "logic 1", "logic 0", "no change" and "toggle".

#### **Basic JK Flip Flop circuit and symbol:**

|                    | Clock | k Input |           | Output |   | Description |  |

|--------------------|-------|---------|-----------|--------|---|-------------|--|

|                    | Clk   | J       | к         | Q      | Q | Description |  |

|                    | х     | 0       | 0         | 1      | 0 | Memory      |  |

| same as<br>for the | х     | 0 0 0 1 | no change |        |   |             |  |

| SR Latch           | -↓_   | 0       | 1         | 1      | 0 | Reset Q » 0 |  |

|                    | х     | 0       | 1         | 0      | 1 | Keset Q » 0 |  |

|                    | -↓_   | 1       | 0         | 0      | 1 | Set Q » 1   |  |

|                    | х     | 1       | 0         | 1      | 0 | Set Q » I   |  |

| toggle             | -↓_   | 1       | 1         | 0      | 1 | Toggle      |  |

| action             | -↓_   | 1       | 1         | 1      | 0 | TOggle      |  |

**Figure 4.5:** The Truth Table for the JK Function

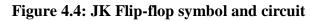

#### 3) <u>D Flip-flop:</u>

The **D** Flip Flop is by far the most important of all the clocked flip-flops. D Flip-flops are used as a part of memory storage elements and data processors as well. D flip-flop can be built using NAND gate or with NOR gate. Due to its versatility, they are available as IC packages. The major applications of D flip-flop are to introduce delay in timing circuit, as a buffer, sampling data at specific intervals. D flip-flop is simpler in terms of wiring connection compared to JK flip-flop. Here we are using NAND gates for demonstrating the D flip flop.

By adding an inverter (NOT gate) between the Set and Reset inputs, the S and R inputs become complements of each other ensuring that the two inputs S and R are never equal (0 or 1) to each other at the same time allowing us to control the toggle action of the flip-flop using one single D (Data) input. Then this Data input, labelled "D" and is used in place of the "Set" signal, and the inverter is used to generate the complementary "Reset" input thereby making a level-sensitive D-type flip-flop from a level-sensitive SR-latch as now S = D and R = not D as shown.

**Basic D Flip Flop circuit and symbol:**

Figure 4.6: D Flip-flop symbol and circuit

A simple SR flip-flop requires two inputs, one to "SET" the output and one to "RESET" the output. By connecting an inverter (NOT gate) to the SR flip-flop we can "SET" and "RESET" the flip-flop using just one input as now the two input signals are complements of each other. This complement avoids the ambiguity inherent in the SR latch when both inputs are LOW, since that state is no longer possible.

Thus, this single input is called the "DATA" input. If this data input is held HIGH the flip flop would be "SET" and when it is LOW the flip flop would change and become "RESET". However, this would be rather pointless since the output of the flip flop would always change on every pulse applied to this data input.

To avoid this an additional input called the "CLOCK" or "ENABLE" input is used to isolate the data input from the flip flop's latching circuitry after the desired data has been stored. The effect is that D input condition is only copied to the output Q when the clock input is active. This then forms the basis of another sequential device called a **D Flip Flop**.

The "D flip flop" will store and output whatever logic level is applied to its data terminal so long as the clock input is HIGH. Once the clock input goes LOW the "set" and "reset" inputs of the flip-flop are both held at logic level "1" so it will not change state and store whatever data was present on its output before the clock transition occurred. In other words, the output is "latched" at either logic "0" or logic "1".

| Clk   | D | Q |   | Description         |

|-------|---|---|---|---------------------|

| ↓ » O | х | Q | Q | Memory<br>no change |

| ↑ » 1 | 0 | 0 | 1 | Reset Q » 0         |

| ↑»1   | 1 | 1 | 0 | Set Q » 1           |

**Figure 4.7:** The Truth Table for the D Function

Note that:  $\downarrow$  and  $\uparrow$  indicates direction of clock pulse as it is assumed D-type flip flops are edge triggered

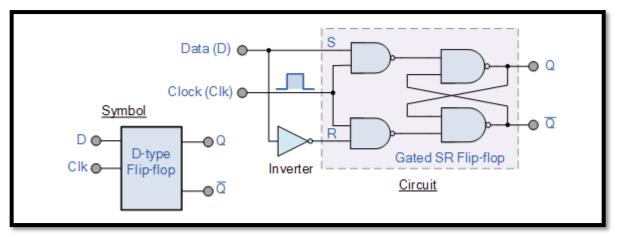

### 4)<u>T Flip-flop</u>

While the *Data* (D) flip-flop is a variation of a clocked SR flip-flop constructed using either NAND or NOR gates, the *Toggle* (T) flip-flop is a variation of the clocked JK flip-flop. The toggle or T-type flip-flop gets its name from the fact that its two outputs Q and Q invert from their previous state as it toggles back and forth every time it is triggered (T = 1).

The Toggle schematic symbol has two inputs available; one represents the "toggle" (T) input and the other the "clock" (CLK) input.

This modified form of the JK flip-flop is obtained by connecting both inputs J and K together. It has only one input along with the clock input. It inverts the state of the outputs each time the input pulse applied to line T passes from the state 1 to the state.

**Basic T Flip Flop circuit and symbol:**

Figure 4.8: T Flip-flop symbol and circuit

| Clock | INPUT  |   | OUTPUT    |       |

|-------|--------|---|-----------|-------|

|       | RESET  | т | Q         | Q'    |

| x     | LOW    | × | 0         | 1     |

| HIGH  | HIGH   | 0 | No Change |       |

| HIGH  | HIGH   | 1 | Toggle    |       |

| LOW   | HIGH X |   | No Cl     | hange |

#### Figure 4.9: The Truth Table for the T Function Procedure:

#### **1.Implementation and Analysis of a R-S Flip-flop**

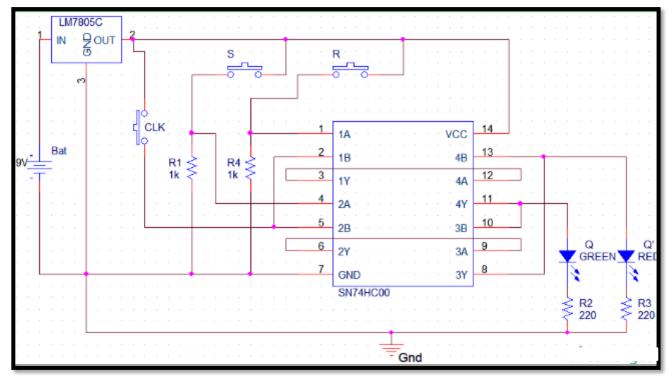

- Carry out a flip-flop type R-S either using NAND ports 7400 IC or **SN74HC00N** IC by looking into schematic provided.

- Connect the SET and RESET inputs to two switches.

- Connect the outputs Q and Q to two LEDs.

- Turn the SET input, with the switch, to 1 and then to 0.

- Analyze the behavior of the outputs.

- Set the RESET line to 1, and then to 0.

- Analyze the behavior of the outputs again.

- Repeat sometimes the operations with the switches and check the carried-out memorizations.

Now, try to set both inputs to 1 and explain what the reason of the uncertain state is.

Figure 4.10: RS Flip-flop schematic diagram

#### **Observation:**

| S | R | Q | Q` |

|---|---|---|----|

| 0 | 0 |   |    |

| 0 | 1 |   |    |

| 1 | 0 |   |    |

| 1 | 1 |   |    |

#### 2. Implementation of negative edge J-K Flip-flop

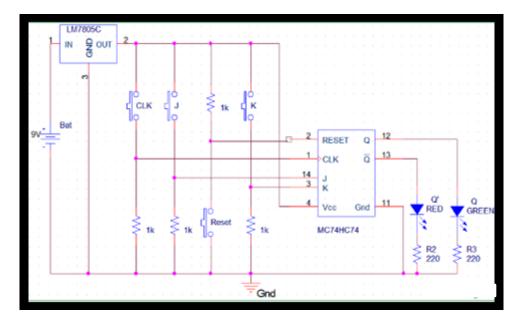

- Carry out the circuit of a flip-flop type by using MC74HC73A according to the given schematic diagram

- Connect the inputs J and K to two switches, and the outputs to two LEDs.

- Set the switches connected to the inputs alternatively high.

- Analyze the behavior of the LEDs.

- Now, set both switches to the logic level 1, and explain the behavior of the flip-flop.

Figure 4.11: J-K Flip-flop schematic diagram

### **Observation:**

| J | Κ | Q | Q` |

|---|---|---|----|

| 0 | 0 |   |    |

| 0 | 1 |   |    |

| 1 | 0 |   |    |

| 1 | 1 |   |    |

#### 3. Implementation of D Flip-flop

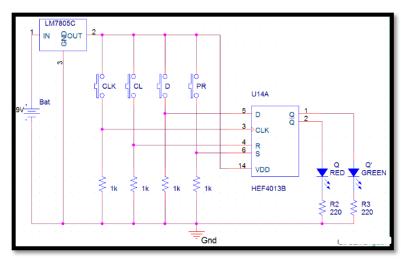

- Carry out the circuit of a flip-flop type D by means IC **HEF4013B** by looking into the schematic

- Connect the inputs P and R to 1.

- Check the operation of the fip-flop D by means of switches 0-1 of the input D and the Clock.

Figure 4.12: D Flip-flop schematic diagram

## **Observation:**

| D | Q |

|---|---|

|   |   |

|   |   |

#### 4. Implementation of T- Flip-flop

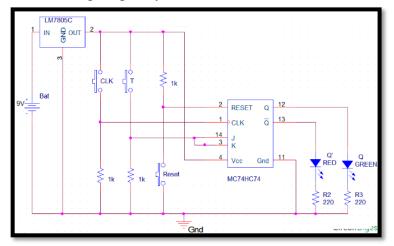

- Carry out the circuit of a flip-flop type T by means of J-K flip-flop according to the given schematic diagram

- Check the operation of the flip-flop T by means of switches 0-1 to the Clock input

Figure 4.13: T Flip-flop schematic diagram

## **Observation:**

| Т | Q |

|---|---|

|   |   |

|   |   |

#### NED University of Engineering & Technology Department of \_\_\_\_ELECTRONIC\_\_ Engineering Course Code and Title: \_\_\_\_EL-408 VLSI System Design\_\_\_\_\_

|                                                                                                                                                        | Psychomotol                                                                                                     |                                                                                                                         | nent Rubric-Level                                                                                                       |                                                                                                                           |                                                                                                                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Skill Sets                                                                                                                                             |                                                                                                                 | Extent of Achievement                                                                                                   |                                                                                                                         |                                                                                                                           |                                                                                                                   |  |  |  |

|                                                                                                                                                        | 0                                                                                                               | 1                                                                                                                       | 2                                                                                                                       | 3                                                                                                                         | 4                                                                                                                 |  |  |  |

| <b>Equipment Identification</b><br>Sensory skill to <i>identify</i><br>equipment and/or its<br>component for a lab work.                               | Not able to identify the equipment.                                                                             |                                                                                                                         |                                                                                                                         |                                                                                                                           | Able to identify<br>equipment as well<br>as its components                                                        |  |  |  |

| Equipment Use<br>Sensory skills to<br><i>demonstrate</i> the use of the<br>equipment for the lab<br>work.                                              | Doesn't<br>demonstrate the<br>use of equipment.                                                                 | Slightly<br>demonstrates the<br>use of equipment.                                                                       | Somewhat<br>demonstrates the<br>use of equipment.                                                                       | Moderately demon<br>strates the use of<br>equipment.                                                                      | Fully<br>demonstrates the<br>use of equipment.                                                                    |  |  |  |

| <u>Procedural Skills</u><br><i>Displays</i> skills to act upon<br>sequence of steps in lab<br>work.                                                    | Not able to either<br>learn or perform<br>lab work<br>procedure.                                                | Able to slightly<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to somewhat<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to moderately<br>understand lab<br>work procedure<br>and perform lab<br>work.                                        | Able to fully<br>understand lab<br>work procedure<br>and perform lab<br>work.                                     |  |  |  |

| Response<br>Ability to <i>imitate</i> the lab<br>work on his/her own.                                                                                  | Not able to<br>imitate the lab<br>work.                                                                         | Able to slightly imitate the lab work.                                                                                  | Able to somewhat<br>imitate the lab<br>work.                                                                            | Able to moderately<br>imitate the lab<br>work.                                                                            | Able to fully<br>imitate the lab<br>work.                                                                         |  |  |  |

| <b>Observation's Use</b><br><i>Displays</i> skills to use the<br>observations from lab<br>work for experimental<br>verifications and<br>illustrations. | Not able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Slightly able to<br>use the<br>observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. | Somewhat able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Moderately able to<br>use the<br>observations from<br>lab work for<br>experimental<br>verifications and<br>illustrations. | Fully able to use<br>the observations<br>from lab work for<br>experimental<br>verifications and<br>illustrations. |  |  |  |

| Safety Adherence<br>Adherence to safety<br>procedures.                                                                                                 | Doesn't adhere to safety procedures.                                                                            | Slightly adheres<br>to safety<br>procedures.                                                                            | Somewhat<br>adheres to safety<br>procedures.                                                                            | Moderately adheres<br>to safety<br>procedures.                                                                            | Fully adheres to safety procedures.                                                                               |  |  |  |

| Equipment Handling<br>Equipment care during the<br>use.                                                                                                | Doesn't handle<br>equipment with<br>required care.                                                              | Rarely handles<br>equipment with<br>required care.                                                                      | Occasionally<br>handles<br>equipment with<br>required care.                                                             | Often handles<br>equipment with<br>required care.                                                                         | Handles<br>equipment with<br>required care.                                                                       |  |  |  |

| Group Work<br>Contributes in a group<br>based lab work.                                                                                                | Doesn't<br>participate and<br>contribute.                                                                       | Slightly<br>participates and<br>contributes.                                                                            | Somewhat<br>participates and<br>contributes.                                                                            | Moderately<br>participates and<br>contributes.                                                                            | Fully participates and contributes.                                                                               |  |  |  |

| Laboratory Session                                                                                                                                     |                                                                                                                 |                                                                                                                         | Dat                                                                                                                     |                                                                                                                           |                                                                                                                   |  |  |  |

| Weighted CLO (Psychomotor Score)  |  |

|-----------------------------------|--|

| Remarks                           |  |

| Instructor's Signature with Date: |  |

## LAB SESSION NO 05

#### **Objective:**

#### To imitate 2-bit counter circuit.

#### Apparatus:

- MC74HC73A (Dual JK flip-flop)

- HEF4013B (Dual D flip-flop)

- LM7805

- Supply

- LEDS

- Resistor sheet

- Breadboard

- Connecting wires

- 7400 IC (NAND)

- Function generator

- Oscilloscope

### **Theory:**

#### **Counters:**

Counters are digital integrated devices which can state in a well-defined sequence, applying a train pulse across the input. A counter is a circuit consisting of a number of Flip Flop and gates working together to count the number of clock pulses applied to its input. Such counters are used in digital clocks, frequency counters, digital voltmeters, digital computers, and numerous other applications. These counters are also called 'BINARY COUNTERS' and can be used apart as counters as frequency dividers, supplying the o/p with a pulse after 'n' input pulses.

If we apply a fixed frequency pulse train to a counter, rather than individual pulses coming at random intervals, we begin to notice some interesting characteristics and useful relationships between the input clock signal and the output signal.

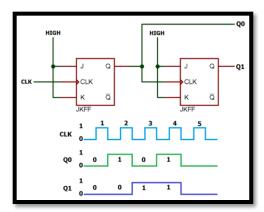

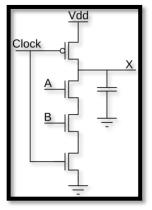

#### **<u>Ripple Counter (Asynchronous):</u>**

A ripple counter is a serial counter. The clock input is applied to only the first of the series of the Flip Flop. Clock pulses for the other Flip Flop come from the preceding Flip Flop. Thus, the clock pulse "ripple" through the circuit in a series fashion. Such circuit is also called asynchronous since the only pulse required for the operation is the clock pulse. The JK Flip Flop have the J and K inputs both tied high, which allows them to toggle with each input pulse. The below figure shows a 2-bit ripple counter.

Figure 5.1: 2-bit ripple counter

Consider a single flip flop with a continuous succession of above. We note three useful facts about the output signals seen at Q and Q':

- a) They are exactly inverted to each other

- b) They are perfect square waves (50% duty cycle)

- c) They have a frequency just half that of the clock pulse train.

Figure 5.2: 2-bit ripple counter symbol

#### **Procedure:**

#### **<u>2-bit Asynchronous Counter:</u>**

• Carry out the circuit of a 2-stage asynchronous counter

- Connect all inputs, J and K to logic 1 (i.e., +5V)

- Connect 1Hz clock to input CK of first flip-flop

- Connect Q0 to CK of second flip-flop

- Connect the two outputs, Q0 and Q1, to oscilloscope

- Power the circuit and analyze the operation of complete system.

## **Outcome:**

#### NED University of Engineering & Technology Department of \_\_\_\_ELECTRONIC\_\_ Engineering Course Code and Title: \_\_\_\_EL-408 VLSI System Design\_\_\_\_\_

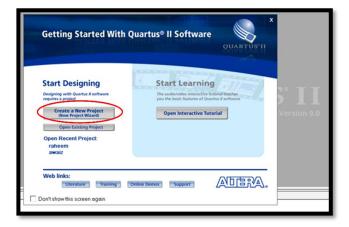

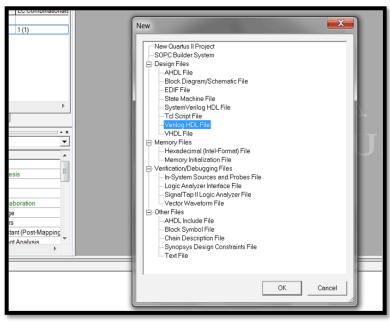

| Psychomotor Domain Assessment Rubric-Level P3                                                                                                          |                                                                                                                 |                                                                                                                         |                                                                                                                         |                                                                                                                           |                                                                                                                   |  |  |